What you’ll learn:

- It’s extremely difficult to create an interconnect for complex SoCs.

- Building an interconnect requires a huge budget and a lot of engineering talent.

- Purchasing interconnect IP gives a company a head start meeting the Functional Safety and ISO 26262 requirements.

System-on-chip (SoC) technology is quickly evolving as the market demands higher computing power, faster speeds, scalability, and better reliability. SoC devices are currently being deployed in a diverse range of applications commonly found in embedded systems once dominated by microcontrollers.

Network-on-a-chip (NoC) provides a full functioning subsystem vital to SoC technology (Fig. 1). Having the right intellectual property (IP) interconnects to enable the required scalability and performance of today’s NoC and SoC designs is critical. However, an ongoing discussion among the design architecture community centers on whether it’s better to purchase SoC interconnect IP from experts or build and maintain interconnect IP in-house.

Effective Interconnect IP Solutions

SoC applications have rapidly changing requirements that must be quickly addressed through the on-chip interconnect, but most interconnects developed in-house weren’t developed to be user-friendly. Given the huge fixed development costs, doing a few chips a year usually makes no economic sense.

Most design teams have adopted a platform approach where one design is adapted for multiple markets and use cases by quickly creating derivative chips. The interconnect is critical to creating these derivative semiconductors. Failure to have a world-class interconnect IP slows down the ability to adapt to new chip requirements and severely limits a company’s ability to respond to market changes.

Interconnect technology is challenging to create and support because of the low power, latency, data path, and security parameters that all must be optimized. In the highly competitive and rapidly changing IC market, companies have better ways to use their talent and money.

Given the complexities, regulations, evolving requirements, and cost, it’s almost always better to license commercially developed interconnect IP. Buying proven technology helps to avoid being stuck supporting IP through multiple iterations and generations. IP experts exclusively focus on creating interconnect IP. These IP packages also allow for custom configuration.

NoC Design: A Tricky Route

If chip companies are still tempted to move forward with their own interconnect IP program, consider what it takes to develop NoC interconnects.

NoC technology is a communication subsystem between modules on an SoC chip. NoC essentially connects IP design blocks on the SoC. The benefits of using a NoC interconnect include its packetized approach, wire reduction leading to less chip real estate, and a significant power demand reduction. NoC also provides a more standardized way to add or replace IPs when designing an SoC.

The most challenging aspect of this process is designing the NoC so that the packets reach their destination at the time they need to arrive—without blowing up the area and/or power. This requires three completely separate skillsets:

- The networking expert to break down packets, channels, and quality of service.

- The semiconductor expert needed for design, verification, and Verilog expertise to design down to the gate level.

- The software expert who creates the IP configuration cockpit that turns chip architects’ system requirements into synthesizable NoC RTL, testbenches, SystemC performance models, IP-XACT data, and other deliverables required of all commercial semiconductor design IP.

The Rapidly Evolving SoC Market

Today’s chip market is changing more rapidly than designers can adapt—as soon as one NoC is done, new requirements come into play. Teams must start the next chip iteration to meet new requirements for performance, bandwidth, cache coherence, arbitration, latency, quality of service, power management, and security.

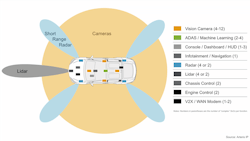

Nowhere is this as accelerated as in vehicle design, where the shift toward autonomous vehicles sees advances in sensing, communications, and artificial intelligence (Fig. 2).

A new interconnect could take over a year to define and implement in league with the rest of the IC design team, and that’s too long—the competition would have already made it to market.

Selling into automotive, medical, or automation markets, safety accessors are going to look closely at how the IC has been built. This means the interconnect team needs traceability, proper verification, and documentation—lots of documentation, or no one will buy the chip. Having a licensed NoC from a partner tightly coupled with key IP vendors is a safer and faster route.

Once the decision is made, licensing the NoC IP from a specialized interconnect developer is the better route from both a technical and business perspective.

Specialization in Functional Safety

Functional safety is the perfect example of a value-add at the IC level for autonomous-vehicle and robot designs, and one that requires training, knowledge, and manpower to complete accurately. It’s better handled by a specialty NoC provider who has worked closely with processor IP providers such as Arm (Fig. 3).

There are many possible safety mechanisms within the interconnect providing diagnostic coverage and managing recoverability and reboots. Among them is the creation of safety islands that have high diagnostic coverage metrics to enable system-level ISO 26262 ASIL D compliance (Fig. 3, again).

These safety islands aid in ensuring fail-safe modes, while ECC and parity transport minimize errors. Much work goes into redundancy and path optimization, as well as subsystem reset and reboot, while avoiding catastrophic failure.

Conclusion

Effective interconnect IP design requires extensive technical expertise in several disciplines. Engineering SoC interconnects in-house will require tens of engineers and prolonged design time, extensive internal verification, and the ability to rapidly address company-wide support concerns and numerous other issues that will only worsen as SoC technology continues to evolve. The alternative to in-house interconnect design is simple: Seek out companies that focus on engineering and licensing the state of the art in NoC interconnect IP.

Benoit de Lescure is CTO of Arteris IP.

About the Author

Benoit de Lescure

CTO, Arteris IP

Benoit de Lescure, CTO of Arteris, has over 20 years of experience in interconnect IP as well as in ASIC engineering. He joined Arteris IP in 2013. Benoit is an inventor on seven patents and earned a postgraduate certificate in microelectronics from the Université Paris VI – Pierre et Marie Curie (UPMC).