PCI Express Gen 5 in the Homestretch

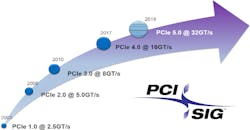

PCI-SIG’s PCI Express (PCIe) Gen 3 is ubiquitous and PCI Express Gen 4, which was finalized in October 2017, pushes data at a rate of 16 Gtransfers/s. PCIe Gen 5 looks to double this to 32 Gtransfers/s (Fig. 1). To handle these high speeds, PCI Express Gen 5 will employ 128/130-bit encoding with scrambling. This was also used in Gen 3 and Gen 4. The encoding reduces electromagnetic interference (EMI) by not applying repeating data patterns in the data stream. PCI Express Gen 1 and Gen 2 used 8/10-bit encoding.

1. PCI Express Gen 5 will double the throughput of PCIe 4.0.

Initially, PCI Express Gen 5 will show up in servers to handle 400-Gb/s Ethernet and dual-channel 200-Gb/s InfiniBand. PCI Express-based storage, like NVMe (Fig. 2), will also benefit from higher throughput. Higher throughput means that fewer links can be used to provide similar throughput of prior incarnations. Furthermore, it will increase the throughput from CPUs and GPUs while retaining the same number of pins. A x16 PCIe Gen 5 connection has a total bandwidth around 128 GB/s.

2. PCI Express storage, using the NVMe protocols, can take advantage of higher throughput. The M.2 (left), U.2 (center), and PCIe card (right) form factors all support NVMe.

Servers are already clamoring for higher bandwidth while consumer hardware is just starting to get PCIe 4 support. High-end embedded applications are on par with servers in terms of bandwidth need. However, the bulk of embedded applications are faring will with low lane count where PCIe Gen 5 would be overkill.

At this point, the PCIe Gen 5 spec revision 0.7 spec was released in May 2018. This provides a complete functional specification. Part of the challenge in its design was maintaining backward-compatibility. The final draft, version 0.9, will get PCI-SIG members to lock down the standard for its final 1.0 release, expected in 2019.

Test and measurement solutions for PCIe Gen 4 are being tuned to handle PCIe Gen5. Teledyne LeCroy’s Summit M5x PCIe Protocol Analyzer/Jammer will handle PCIe Gen 4 and Gen 5. It was the first to handle PCIe Gen 4. It’s capable of modifying, replacing, inserting, and deleting traffic between a PCIe root complex and PCIe endpoint. This allows developers to verify adherence to the standard as well as help in debugging potential errors in protocol behavior.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: