11 Myths About Floating-Poly Embedded Flash

This file type includes high-resolution graphics and schematics when applicable.

The automotive industry has been fueling growth and innovation in the semiconductor industry for several years. According to market research firm IHS, the automotive semiconductor market has surpassed $30B in annual revenue and continues to climb with the addition of advanced driver assistance systems (ADAS) and the push for fuel efficiency and added convenience. The value of semiconductor content in each of today’s luxury cars is about $1000 USD and about $350 USD in a mid-range car, and automotive MCUs are a significant portion of that.

Most of the automotive MCUs have on-chip embedded flash, which contains a complex and exhaustive instruction code. Despite the fact that floating-poly-based embedded flash is deployed widely across a series of products for automotive, industrial and consumer applications, and it’s a paragon of non-volatile memory technologies, several myths pertaining to embedded-flash technologies need to be debunked.

1. OTP can replace embedded flash for instruction-code applications.

Some integrated circuits need to be programmed with an on-chip instruction code only once, and this programming can be done either during wafer-sort or in-package during final testing before shipping the IC to the client, or done in-field. Although the one-time-programming (OTP) requirement of the non-volatile memory appears to be adequately satisfied with an OTP solution, in practice it has some serious user-experience and reliability issues.

First, OTP programming for a large memory block is fraught with intractable low-yield challenges, which requires use of multiple redundant bits and associated redundancy-management circuitry. This added complexity is a headache for chip designers. Second, a large block of OTP solution in general doesn’t offer data-retention time that’s competitive with the same offered by a specialized embedded-flash process optimized for long-term data reliability. This is because the uncontrolled programming variations on a large OTP memory block tend to have tail bits that pose difficulties in reading accuracy.

2. Embedded flash is expensive.

Most of the time, you get what you pay for. On the surface, it seems like a floating-poly embedded-flash solution is more expensive compared to a charge-trap-based solution (such as SONOS), because floating-poly embedded flash typically requires more masking steps compared to a charge-trap-based, embedded non-volatile memory solution.

However, chip designers should carefully consider the total cost of the non-volatile solution, including potential yield loss, distress due to field-returns, long-term data retention, total chip area (including the required ECC and redundant circuits), and time to production. In addition, a charge-trap-based solution isn’t suitable for high-temperature and high-endurance applications.

Therefore, if a non-volatile memory platform must meet the need for a series of low-end and high-end applications, it’s more desirable to have a non-volatile memory solution that fits all applications on a wide range of voltage, operating temperature, data retention, and endurance. Having multiple non-volatile platforms for one technology node is significantly more expensive than having a reliable floating-poly-based, non-volatile memory solution.

3. Embedded flash isn’t available at foundries’ leading technology nodes.

Generally, embedded flash is two generations behind the leading technology node, and it’s primarily driven by the demand for non-volatile memory solutions. Meanwhile, advanced nodes such as 14-nm FinFET are being driven by high-end SoCs, high-performance computing, and graphics processors, which don’t require an on-chip embedded flash.

Recently, embedded flash has taken huge leaps in terms of its availability at advanced logic nodes. In 2012, embedded flash at pure-play foundries was only available at 90 nm. But, in the last four years, embedded-flash availability is reaching 28 nm at many leading foundries, and is being developed for high-end automotive and IoT solutions. This huge leap in development was primarily driven by automotive applications, which are driving the demand of automotive MCUs on advanced technology nodes.

4. Embedded-flash memory doesn’t scale.

Ten years ago, the word on the street was that embedded flash is dead at sub-90-nm nodes because of the perceived difficulty and challenges in scaling the bitcell.That perception has been proven wrong, since embedded-flash is already in development at 28 nm. The challenge today is to scale embedded flash to FinFET process generations. There are, however, foundries such as Samsung and GLOBALFOUNDRIES focusing on fully depleted silicon-on-insulator (FDSOI) technology on planar 22-nm technology nodes and possibly beyond, which may extend the life of embedded flash past the 28-nm node.

5. Only a few foundries have embedded-flash technology available.

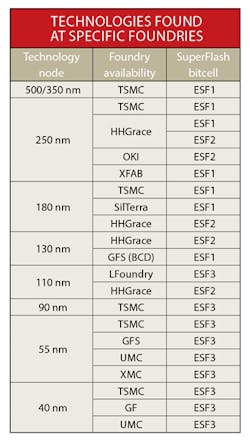

Automotive, mobile, and IoT applications are fueling the growth of microcontrollers and other flash-enabled devices, which has led to the flash-enabled market ballooning to ~$22B USD. To play in that market segment, many foundries either have enabled embedded-flash platforms or are actively working on implementing one, including GLOBALFOUNDRIES, HHGrace, LFoundry, SilTerra, TSMC, UMC, Vanguard, X-FAB, XMC, and more to come (see table).

6. Embedded flash is used in a niche market.

With a $25B application-service-provider (ASP) market, excluding memories, it comprises more than 10% of the semiconductor market, seeing use in devices such as MCUs, smart analog, Bluetooth, power management , SIM and bank cards, flash-enabled SoCs, and IoT applications. Many foundries are implementing the platform because of the ever-growing demand created for this technology.

7. Embedded flash is adopted by only pure-play foundries.

All fabless and many fablite integrated device manufacturers (IDMs) have products manufactured at pure-play foundries. However, IDMs have their own manufacturing facilities as well, and depending on the product set and technology availability, they may choose to go with either their own facility or outsource to a pure-play foundry. Many top-tier IDMs have chosen to install Silicon Storage Technology’s (SST) Embedded Flash technology at their own foundries so that they can customize and differentiate the technology across a series of technology nodes.

8. Embedded flash doesn’t support EEPROM functionality.

Traditional EEPROM architecture supported byte-write operation and was used by applications requiring frequent data updates. Generally, embedded flash is organized in a group of cells called sectors. A sector needs to fully erased before new data can be written. However, simple design techniques using an SRAM buffer can be used to mimic EEPROM functionality at a fraction of the overall embedded-flash-memory area, and would be transparent to the user.

9. All floating-poly embedded-flash memories are equal.

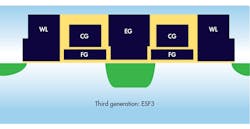

For many years, the majority of IDMs were using a similar 1T floating-poly stacked-gate solution for applications requiring embedded flash. Over the last two decades, the innovative split-gate SuperFlash technology changed the industry with its differentiated and efficient poly-to-poly erase and source-side injection programming bitcell (Fig. 1).

10. Embedded flash doesn’t work at low voltages for IoT applications.

Internet of Things (IoT) applications require low-voltage read/write operation. Even though Program/Erase operation needs high voltage, it’s transparent to the user as the flash macro receives core I/O voltage from the user and employs an internal charge pump to raise the voltage to the required high voltage for Program/Erase. Therefore, embedded flash is ready for low-power IoT applications.

11. Embedded flash can’t meet EEPROM endurance.

Typically, an EEPROM can meet 1M endurance cycles. Historically, most of the MCU and smartcard applications required less than 100K endurance. Recently, though, the more stringent requirements for some applications such as SIM cards have pushed endurance requirements to 500K (typical). To support 500K, the third-generation SuperFlash technology (ESF3) has displayed better endurance characteristics than its predecessor technologies (Fig. 2), and we at SST have plenty of data showing that it can meet 500K endurance for these applications.

About the Author

Vipin Tiwari

Director of Marketing and Business Development

Vipin Tiwari has over 18 years of experience in semiconductor intellectual property, technology licensing, product marketing, engineering management, and memory design. He currently serves as Director of business development and marketing at Silicon Storage Technology Inc. (a Microchip Technology company), leading worldwide business development, technology licensing, contract negotiations, marketing, and application engineering responsibilities.

Before joining SST, Mr. Tiwari held a series of management and design engineering positions at Virage Logic Corp. and ST Microelectronics, and was responsible for product marketing, embedded NVM, embedded SRAM designs, memory compiler development, and place & route. He holds eight U.S. patents and has several more patents pending.

Mr. Tiwari received a Bachelor’s in Electronics Engineering, from IIT-BHU, India, and an MBA from Santa Clara University, Calif.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: