ARM Fills In Midrange With Cortex-A12

ARM expects its 32-bit Cortex-A12 architecture to show up in chips in 2014. It delivers a 40% performance boost over the Cortex-A9 while using the same amount of power. Also, it provides high-end features like big.LITTLE support (see “Little Core Shares Big Core Architecture”), 40-bit addressing for access to 1 Tbyte of virtual memory, security features for hardware virtualization, and ARM’s TrustZone support.

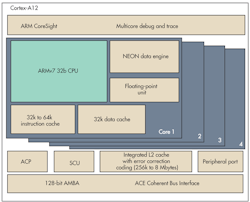

The Cortex-A12 fits between the Cortex-A7/A9 and Cortex-A15, which is the basis for a number of multicore systems-on-chip (SoCs) including Nvidia’s Tegra 4 (see “Quad Cortex-A15 + 72-Core GeForce GPU = Tegra 4”). It fits well below ARM’s 64-bit Cortex-A50 offerings, though the Cortex-A12 will support up to four cores while targeting the latest 28-nm technology (see the figure).

1. ARM’s 32-bit Cortex-A12 supports up to four cores and can be combined with the Mali-T622 or Mali-V500 GPUs.

Related Articles

- Quad Cortex-A15 + 72-Core GeForce GPU = Tegra 4

- Delivering 64-Bit Arm Platforms

- Little Core Shares Big Core Architecture

The architecture was designed from the ground up. It incorporates a dual-issue, out-of-order (OoO), 11-stage, dynamic length pipeline that’s tightly integrated with the NEON SIMD engine and floating-point units. The L1 and L2 caches have been optimized for mobile workloads. Its CPU and GPU cores are connected via a 128-bit AMBA ACE (AXI Coherency Extensions). The Accelerator Coherency Port (ACP) provides I/O coherency for DMA units.

The chips will include an ARM peripheral port designed for low-latency peripherals that do not have to utilize the AMBA ACE, eliminating related memory traffic congestion.

The architecture supports the midrange Mali-T622 GPU (see “Mobile GPU Architecture Supports Emerging Compression Standard”). This second-generation GPU supports OpenCL 1.1, Renderscript Compute, and OpenCL ES 3.0. The Cortex-A12 also can be paired with the Mali-V500 video engine, which includes up to eight cores. It can handle 1080p 60-Hz HD video encode and decode and is scalable to 4K120. It also supports AFBC (ARM frame buffer compression), which can reduce bandwidth by 50%. It supports a TrustZone secure video path for content protection as well.

The Cortex-A12 comes with Processor Optimization Pack (POP) IP support that was used with the Cortex-A50 family and the Cortex-A7, Cortex-A15, Cortex-A5, and Cortex-A9. For big.LITTLE support, the Cortex-A12 will be paired with a Cortex-A7 core. It provides a lower-cost, lower-power solution to a Cortex-A15/A7 pairing.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: