Platform Security Processor Protects Low Power APUs

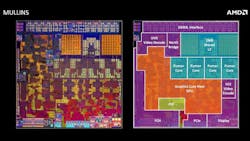

AMD's Platform Security Processor (PSP) (Fig. 1) is being incorporated into its latest line of low power Accelerated Processing Units (APU) that combine CPU and GPU cores on the same chip (see “APU Blends Quad Core x86 With 384 Core GPU”). These include the “Beema” and “Mullins” chips based on the Puma+ x86 cores that are combined with GPUs based on AMD's Graphics Core Next (GCN) architecture. While this is the latest GPU technology these chip families do not employ the latest Heterogeneous System Architecture (HSA) that provides a unified virtual memory environment (see “Heterogeneous System Architecture Changes CPU/GPU Software”).

Related Articles

- Heterogeneous System Architecture Changes CPU/GPU Software

- APU Blends Quad Core x86 With 384 Core GPU

- Low Power, Single-Chip APU Delivers High Performance

- APU Targets Embedded Applications

- Cortex-A5 Kit Targets Mobile Multimedia Applications

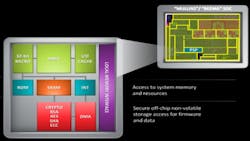

The PSP is based on an ARM Cortex-A5 core (see “Cortex-A5 Kit Targets Mobile Multimedia Applications”). This implements ARM's TrustZone technology that has been utilized in a wide range of ARM cores. In this case though, it is protecting the x86 core. This secure core boots first using its own ROM and SRAM and verifies the code that boots the x86 core. Custom OS support is available from Trustonics. The PSP's cryptographic co-processor can support x86 applications to secure off-chip storage.

Security is not the only new features found in the Beema and Mullins chips. The energy aware battery boost technology exploits race-to-idle behavior. In many cases, running faster for a shorter period of time is more power efficient that running for a longer period of time using a lower power setting. This is on top of a 20% lower idle power level.

Beema and Mullins (Fig. 2) are built on 28-nm technology. Beema targets entry level notebooks while Mullins is designed for tablets. The have up to four x86 Puma+ cores and a 128 GCN Radeon GPU. Puma+ uses a 2-wide our-of-order execution unit. The chips have a 64-bit memory interface.

These chips will likely host Windows operating systems although they can easily handle Android and Linux as well. The chips support DDR3 memory. The Beema A6-6310 clocks at 2.4 GHz with four cores and a 15 W TDP while the low end, E1 Micro-6200T Mullins runs at 1.4 GHz using only 2.95 W TDP with a pair of cores.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: