A Host Of 3D IC Collaborations And Standardization Efforts Emerging

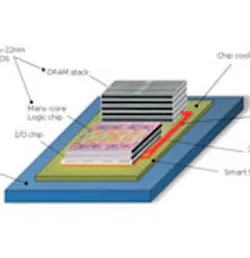

There’s a beehive of global activity among semiconductor IC manufacturers, equipment and materials suppliers, process and packaging experts, and research centers and universities, all trying to get a jump on producing true 3D ICs using through-silicon vias (TSVs) through refinements, standardization, and collaborations.

Four groups within Semiconductor Equipment and Materials International (SEMI) are working on 3D IC standards. Its Three-Dimensional Stacked Integrated Circuits Committee includes SEMI members Globalfoundries, Hewlett-Packard, IBM, Intel, Samsung, United Microelectronics Corp. (UMC), Amkor, ASE, Europe’s Interuniversity Microelectronics Center (IMEC), Asia’s Industrial Technology Research Institute (ITRI), Olympus, Qualcomm, Semilab, Tokyo Electronics, and Xilinx. Many of these companies are collaborating on specific goals.

Taiwan-based ITRI sponsors a 3D consortium that has nearly two dozen members. Many of these members are promising end-to-end 3D IC foundry services that start this year. ITRI and Rambus Inc. are collaborating on the development of interconnect and 3D packaging technologies. In addition, Rambus has joined the Advanced Stacked-System Technology and Application Consortium (Ad-STAC), a multi-national research association led by ITRI for developing silicon interposer technology.

The Joint Electron Device Engineering Council is pioneering a Wide I/O standard specification for 3D ICs. The specification will support 512-bit-wide TSVs.

Singapore-based A*STAR Institute of Microelectronics (IME) and 3D IC developer Tezzaron Semiconductor have agreed to develop and exploit advanced through-silicon interposer technology, with near-term efforts aimed at developing such interposers for micro-electromechanical systems (MEMS) and silicon photonics.

STMicroelectronics is working with France’s CEA-LETI and silicon interposer manufacturer Shinko Industries Co. to smooth the transition from 2.5D to 3D ICs. The three are prototyping devices at a 300-mm wafer fabrication facility and expect to have commercially available devices this year. Also, Japan’s Elpida Memory Co. has reported progress on developing a 3D 2-Gbit DDR3 DRAM using high-density TSVs while working with Powertech Technology and UMC.

IMEC is collaborating with Microtech Inc. on perfecting the testing and characterization of 3D ICs. Germany’s IZM research institute Fraunhofer AZM says it’s ready to integrate processor memory, logic, analog, MEMS, and RF chips into 3D ICs by 2014. IMEC’s INSITE program builds on the institute’s vast knowledge and capabilities in process technology and extends it to path-finding methodologies to co-explore technology options and system design.

In a surprising development, silicon IC foundry giant Taiwan Semiconductor Manufacturing Company (TSMC) has decided to go it alone in developing 3D IC chip stacking technology and will offer its capabilities only to future customers. This approach is bound to limit available foundry services for fabless chip designers. TSMC believes its approach will be simpler, cheaper, and more reliable than using multiple foundries, packaging houses, and other partners and will be focused on TSVs early on in the process, adding packaging capabilities later.

Analog Devices, LSI Corp., ON Semiconductor Corp., and Qualcomm Inc. have joined SEMATECH’s 3D Enablement program based at the College of Nanoscale Science and Engineering (CNSE) of the University at Albany, N.Y. They will join CNSE, Global Foundries, Hewlett-Packard, Hynix, IBM, Samsung, Intel, and UMC to extend the program’s position as a broad, cohesive initiative and to enable industry wide ecosystem readiness for cost-effective TSV-based 3D stacked IC solutions. This includes identifying critical 3D IC technology needs and the development of path-finding capabilities, EDA tools, and appropriate test vehicles.

The Joint Electron Device Engineering Council (JEDEC), which announced early in 2011 a broad set of standards for 3D ICs, is set to release what is characterized as the first 3D interface IC standard. JEDEC has already released the JEP158 standard for 3D ICs with TSVs and will soon release the WideIO standard, which combines logic and DRAM memory in the same package to reduce interconnect capacitance. It calls for a maximum four-dice stack of memory cube that can interface to system-on-a-chip (SoC) logic with a maximum target package size of 10 by 10 by 1 mm.

In addition, SEMATECH has been active in pointing out looming 3D IC hurdles in need of a solution. Its 3D Enablement Center, together with the Semiconductor Industry Association (SIA) and Semiconductor Research Corporation (SRC), has identified the top technical challenges for new “killer” applications to enable future development of heterogeneous 3D integration.

About the Author

Roger Allan

Roger Allan is an electronics journalism veteran, and served as Electronic Design's Executive Editor for 15 of those years. He has covered just about every technology beat from semiconductors, components, packaging and power devices, to communications, test and measurement, automotive electronics, robotics, medical electronics, military electronics, robotics, and industrial electronics. His specialties include MEMS and nanoelectronics technologies. He is a contributor to the McGraw Hill Annual Encyclopedia of Science and Technology. He is also a Life Senior Member of the IEEE and holds a BSEE from New York University's School of Engineering and Science. Roger has worked for major electronics magazines besides Electronic Design, including the IEEE Spectrum, Electronics, EDN, Electronic Products, and the British New Scientist. He also has working experience in the electronics industry as a design engineer in filters, power supplies and control systems.

After his retirement from Electronic Design Magazine, He has been extensively contributing articles for Penton’s Electronic Design, Power Electronics Technology, Energy Efficiency and Technology (EE&T) and Microwaves RF Magazine, covering all of the aforementioned electronics segments as well as energy efficiency, harvesting and related technologies. He has also contributed articles to other electronics technology magazines worldwide.

He is a “jack of all trades and a master in leading-edge technologies” like MEMS, nanolectronics, autonomous vehicles, artificial intelligence, military electronics, biometrics, implantable medical devices, and energy harvesting and related technologies.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: