HP’s Artist Graphics Chip: Highly Integrated and System-Focused

>> Electronic Design Resources

.. >> Library: Article Series

.. .. >> Series: The Graphics Chip Chronicles

.. .. .. >> Introduction to this Series

.. .. .. << Intel's i740

In 1993, facing heavy competition from Sun Microsystems, HP set the design goal for its new 32-bit HP 9000/712 workstation to hit the performance levels of 1992-era workstations and servers at a fraction of their fabrication costs. Their target was the earlier generation HP 9000/735. To accomplish this, HP employed VLSI technologies for the graphics processor components, which were state-of-the-art at the time.

What they came up with was the heart of the system: the famous PA-RISC CPU. The CPU's equally impressive coprocessor was HP's Artist chip, which replaced the company's CRX window accelerator add-in board (AIB). That board marked the beginning of standardized graphics hardware architecture for window system acceleration.

The CRX marked the beginning of a standardized graphics hardware architecture for window system acceleration. The architecture was chosen for its simplicity of implementation and for the clean model it presented to the software driver developers. One of HP’s most important design decisions was to accelerate key primitives only—a RISC approach. Many earlier controllers chose to accelerate a large gamut of graphical operations, such as ellipses and arithmetic pixel operations. Graphics subsystems designed with these controllers were typically expensive and exhibited only moderate window system performance. In the CRX and subsequent accelerators, including the Model 712’s graphics chip, HP decided to accelerate a smaller but carefully chosen set of primitives, which are described in the following sections.

When the engineers at HP approached the problem of reducing costs, there were three major areas the chip was intended to address (in order of priority):

- Fast 2D GUI

- Digital video decompression support—both locally and over LAN/WAN

- Efficient 3D graphics

In addition, the designers included:

- Vector, rectangle, framebuffer bitBLT, text cursor hardware

- Bit/pixel framebuffer access mode, VRAM block write

- Boolean raster operations

- Two look-up tables to reduce palette conflict

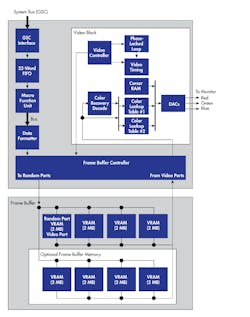

The Artist graphics chip combined a GUI accelerator, a frame buffer controller (32-bits wide), two look up tables (LUTs), video timing, cursor control and an integrated LUT-DAC. The chip was capable of supporting 1 to 2 MB of VRAM and provided 8 bits up to its highest resolution of 1280 × 1024 at 72 Hz non-interlaced refresh. The ninth bit controlled selection of one of the two LUT-DACs. The chip also included a built-in programmable PLL that eliminated the need for a timing crystal.

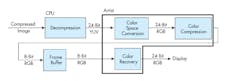

The design balanced the CPU’s strengths with those of the graphics controller, running the video compression and decompression on the CPU while performing color space conversion and compression/decompression on the Artist graphics chip.

HP also developed a proprietary color compression algorithm that could squeeze 24-bit color to 8 bits while preserving the former's look.

The performance of the Artist chip was impressive at the time:

- Large rectangle fill 850 Mpixels/second

- Vectors/second (10-pixel random) 21 M/second

- 10 x 10 rectangles 1.7M/second

- Text (6 x 13 characters/second) 1M

- 3D transformed vectors/second > 1M

- Frame buffer bitBLT (unaligned pixels/second) 47 M

The CPU handled transformations and clipping as well as lighting, z-buffering and pixel color interpolation for polygons. The Artist chip took care of vector rasterizing and color compression into the frame buffer. The chip added 70 ns VRAMs and included a 37.5 nanosecond (ns) page mode speed, using the features of the VRAM for plane mask, extended data out and block copy. As a result, the chip could deliver 850 Mpixels/second for constant-color objects.

The chip had 525,000 transistors, built in 0.8 micron 3-layer (aluminum) HP CMOS26B process. The die size was 9.7 mm by 12.1 mm and HP enclosed it in 208-pin metal QFP or 240 MQFP packages with a flat-panel driver output. The chip had a 40-80 MHz GUI/RAM clock and generated a 25-135 MHz video output—and it only used 3.5 watts (W) in the worst case scenario.

Reduced cost was the primary objective for the graphics chip design. And HP succeeded: the manufacturing cost for the Model 712 graphics subsystem was 1/3 of the cost of the original CRX graphics subsystem. In addition, the entry-level 1024-by-768-pixel version of the graphics chip costs five times less than the CRX subsystem.

These cost reductions were achieved primarily through an aggressive amount of integration. The graphics chip represents the culmination of a series of optimizations of the CRX family, combining almost the entire GUI accelerator onto a single chip. The only major function not integrated was the frame buffer.

The HP Artist chip was one of the first to employ software programmable resolutions. One of the problems with previous workstation graphics subsystems was that they operated at a fixed video resolution and refresh rate. That posed problems in configuring systems at the factory and during customer upgrades.

The Artist graphics chip incorporated an advanced digital frequency synthesizer that generates the clocks necessary for the video subsystem. The synthesizer, which was based on a HP proprietary digital phase-locked loop (PLL) technology, allowed software configurability of the resolution and frequency of the video signal. Thus, alternate monitors could be connected without changing any video hardware. Originally, the chip supported these configurations:

- 640 x 480 pixels 60 Hz, standard VESA timing

- 800 x 600 pixels 60 Hz

- 1024 x 1024 pixels 75 Hz and flat panel

- 1280 x 1024 pixels 72 Hz

As new monitor timings appeared, the graphics chip could be reprogrammed with the parameters associated with the new display.

Summary

HP created its Artist graphics chip with the philosophies of system-level-optimized design. That enabled them to meet their goals of very low manufacturing cost, good performance at their price point, architectural compatibility, and introduction of some important new functionality. The Artist chip was a breakthrough product for HP and served them well for many years.

Conclusion

In the 1980s and early 1990s, semiconductors were laid out on large backlit plotter tables. The layout engineers used to put a signature, or a symbol, a cartoon, or a picture in the pattern somewhere. It was done for three reasons: 1. to sign a work of art; 2. for copyright protection; and 3. because they could. Later, when the layout was done on a computer, many chip designers carried on the tradition.

The above micrograph is a logo that was concealed on an HP chip from the early 1990s. The same chip also featured initials from 20 designers and the hidden message, “If you can read this… you are too damn close!”

>> Electronic Design Resources

.. >> Library: Article Series

.. .. >> Series: The Graphics Chip Chronicles

.. .. .. >> Introduction to this Series

.. .. .. << Intel's i740

About the Author

Jon Peddie

President

Dr. Jon Peddie heads up Tiburon, Calif.-based Jon Peddie Research. Peddie lectures at numerous conferences on topics pertaining to graphics technology and the emerging trends in digital media technology. He is the former president of Siggraph Pioneers, and is also the author of several books. Peddie was recently honored by the CAD Society with a lifetime achievement award. Peddie is a senior and lifetime member of IEEE (joined in 1963), and a former chair of the IEEE Super Computer Committee. Contact him at [email protected].

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: