CXL-Attached Memory Gets Real

What you’ll learn

- What is CXL-attached memory?

- What is memory pooling?

- How Leo Smart Memory Controllers work with processors.

There’s never enough memory. Applications like cloud computing need as much as they can get. Processors tend to support a few banks of DRAM, and linking multiple processors together helps boost the amount of memory. Nonetheless, more is needed.

PCI Express is the de facto peripheral standard. Built on top of the latest standard is the Compute Express Link (CXL) standard, now in its third incarnation. It can be used to connect processors of all types and memory in a single memory space, allowing pools of memory to be allocated among compute resources.

Such a hyperscaler approach is where cloud computing is going, and it will be applicable to large embedded systems as well. Systems can create partitions with the required amount of memory, compute, and connectivity from a common pool of resources.

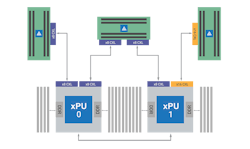

Astera Labs’ Leo Memory Connectivity Platform is designed to support CXL 1.1 and 2.0 (see figure). The Leo Memory Controller chip supports up to 2 TB of memory running at 5600 Mtransactions/s/memory channel. The chip supports JEDEC DDR standards as well as vendor-specific interfaces.

The system also provides server-grade customizable Reliability, Availability and Serviceability (RAS) capabilities. As a result, center operators can customize their systems so that factors such as memory errors, material degradation, environmental impacts, and manufacturing defects don’t impact applications. The telemetry and software APIs support fleet management of cloud-based platforms.

The latest products include the Leo E-Series Smart Memory Controllers that support memory expansion; the Leo P-Series Smart Memory Controllers supporting memory expansion, pooling, and sharing; and the Aurora A-Series Smart Memory Hardware Solutions, which is a PCIe CEM add-in card for plug-and-play deployment.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: