New SerDes Stays a Step Ahead in High-Speed Connectivity

Check out more coverage of DesignCon 2023.

As the world deals with a deluge of data, everyone is trying to move it all faster from Point A to Point B—between chips on a circuit board, over backplanes, or from one end of a cable to the other in the system.

To keep up with the need for speed in data centers and other areas, companies are racing to roll out new generations of one of the most fundamental building blocks for high-speed connectivity: SerDes.

While 28- and 56-Gb/s SerDes is only now becoming more widely used in the switches, servers, and other bandwidth- and power-hungry gear in data centers and wireless networks, 112G SerDes is the state-of-the-art today. But the need for more inter-chip, board, backplane, and inter-system bandwidth is spurring everyone from semiconductor vendors to makers of connectors, cables, and sockets to prepare for 224G.

224G PAM-4 SerDes

Intel is pushing the envelope in high-speed serial connectivity with a new long-reach (LR) 224G PAM-4 SerDes. It displayed a new 5-nm prototype code-named “Falcon” in demos at this year’s DesignCon.

Transceivers with high-speed I/O quickly move data on and off chips such as Intel FPGAs. The high-speed connectivity helps process vast amounts of data everywhere from at the edge to the core to the cloud.

The Santa Clara, Calif.-based company said the 224G transceiver is equipped with blocks of analog-to-digital converter (ADC) and digital-to-analog converter (DAC) digital-signal-processing (DSP)-based SerDes (Fig. 1).

As the speed of signals continues to rise, SerDes has become a battleground for everyone from networking and connectivity chipmakers Broadcom, Credo, Intel, Marvell, and NVIDIA to the likes of IP giant Synopsys.

SerDes is the underlying technology behind a wide range of existing and emerging high-speed connectivity standards in the data center and other markets, from 200- and 400-Gb/s data transmission over Ethernet to 800- and even 1,600-Gb/s data rates that the new SerDes IP would open the door to in the future, said Intel. SerDes also is at the heart of PCI Express (PCIe) and many other industry-standard protocols.

Dealing with Noise

With every generational leap in speed, the distance that the signals can travel over copper traces in a PCB before being scrambled by signal-integrity or electromagnetic-interference (EMI) issues is shrinking.

To keep the problem in check, companies are removing the signals from the copper traces in the circuit board and instead routing them through connectors and “over-the-board” cables to transfer signals over longer distances. The so-called “overpass” connector is mounted close to—or loaded into the same package as—the FPGA or other processor with the SerDes inside. The cable attached to it then transfers the differential SerDes data signal, with the cable usually terminating directly at a socket that sits on the front of a switch.

Test Demo

At DesignCon early this month, Intel partnered with TE Connectivity to test the prototype of the 224G SerDes, based on the 5-nm node from TSMC. TE Connectivity used a new “catapult” connector called AdrenaLINE that was mounted on a circuit board near the Intel-designed SerDes, which routed the PAM-4 signals over half a meter of cable to a separate PCB, despite the connectors causing loss (Fig. 2).

In addition to its ability to handle high-speed connectivity over backplanes and passive cables for Ethernet, Intel’s LR SerDes is designed to support very short reach (VSR) interfaces for chip-to-module (copper or optical) connectivity with a single connector, at distances of up to 0.1 m. The SerDes also meets the requirements for medium reach (MR) for chip-to-chip and midplane connectivity at up to 0.25 m.

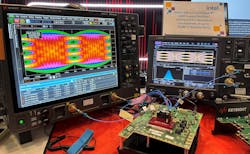

Testing these high-speed signals is a serious challenge the electronics industry is trying to resolve, too. Keysight showed a real-time oscilloscope from its Infinium UXR series capturing signals from Intel’s 224G SerDes as they traversed a test board and then clearly displaying the “eyes” of the signal. The term “eye” refers to the pattern of the signal, as seen on the oscilloscope, as it travels across a PCB or through connectors and cables (Fig. 3).

As 112G is upgraded to 224G SerDes in the future, the data rates double. As a result, it becomes more of a challenge to design systems where the eye stays open. The larger the opening of the eye, the less signal distortion.

Intel said that it has upgraded the SerDes at the heart of its FPGAs from generation to generation, from the 112G SerDes tiles in its flagship Agilex FPGA to the 224G SerDes destined for its future products.

Check out more coverage of DesignCon 2023.

About the Author

James Morra

Senior Editor

James Morra is the senior editor for Electronic Design, covering the semiconductor industry and new technology trends, with a focus on power electronics and power management. He also reports on the business behind electrical engineering, including the electronics supply chain. He joined Electronic Design in 2015 and is based in Chicago, Illinois.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: