Network-on-Chip Gets Automated Timing Closure

Arteris FlexNoC is a Network-on-Chip (NoC) interconnect designed for building high-performance System-on-Chip (SoC) platforms. The use of a third-party NoC interconnect can reduce time to market and result in smaller die sizes that in turn reduces cost. The modular design makes derivative chip design easier as well. It can handle a range of architectures including AXI, OCP, and AHB in addition to proprietary interfaces.

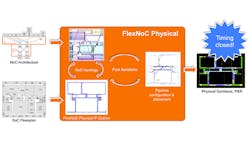

The new FlexNoC Physical product is designed for automated timing closure with FlexNoC designs. It can save as much as three months of work due to timing closures on complex SoC designs (Fig. 1). This in turn reduces the cost of the SoC.

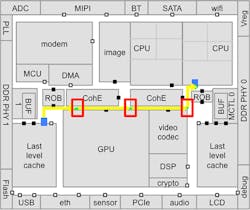

The challenges addressed by FlexNoC Physical are significant because of the tight timing requirements on today’s SoCs. These are often so large that signals cannot move from one side of the SoC to the other in one clock cycle. These designs require timing pipelines to latch data as required by the system timing specifications.

FlexNoC Physical adds timing pipelines automatically as necessary for a given design (Fig. 2). In the past these adjustments were done manually. The auto-pipe approach allows the SoC floorplan to be done early in the design cycle with the NoC timing handled independent of the modules it connects. It also provides a finer-grain implementation because the system does not care how many auto pipes are used or where they are incorporated.

The reason Arteris’ approach is important is because not all SoC designs are possible. There have been a number of large SoC designs that had to be scrapped because the timing requirements could not be met. This was not determined until after all the systems were integrated, because the timing closure was done last.

FlexNoC Physical allows the NoC timing to be locked down early in the design cycle. The final FlexNoC layout with a workable timing closure will allow the final SoC design to be workable (Fig. 3).

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: