Developing a custom micro has a number of advantages. It provides a very flexible design platform that can incorporate more complex algorithms for applications like motor control. This approach also offers better copy protection.

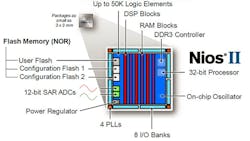

The MAX 10 FPGAs can be utilized without a soft-core processor. It has the usual complement of cells, DSP blocks and I/O. It uses on-chip flash memory to program the FGPA fabric. There are two configuration NOR flash blocks that make the chip ideal for processor-based solutions that might need to handle in-field upgrades. This works like dual BIOS flash systems found on PCs. One flash block can be programmed while the other is in use. The user flash block is where application code for a soft-core processor can reside.

The chips are available with up to 50K logic elements (LE). A NIOS II core fits in as little as 600 cells. A soft, DDR3 DRAM controller could also be part of the mix. This still leaves a lot of logic left for custom peripherals or computational logic.

Many FPGAs are designed for digital chores but the MAX 10 includes a pair of 12-bit, successive approximation register (SAR) analog-to-digital converters (ADC). There is also an on-chip temperature sensor.

Configuration start up time is under 10 ms. A soft-core processor will need additional time to handle application chores.

The MAX 10 can be had in a package as small as 3-mm by 3-mm. At the low end is a 2000 LE unit with only a single configuration flash block. All others have the dual configuration support. The 50K unit has 1638 Kbits of RAM and 512 Kbytes of user flash along with 144 18-bit multipliers.

Altera’s Enpirion power management chip complements the MAX 10. It provides power-up sequencing.

Developers can take advantage of Altera’s Quartus II software to configure the MAX 10. The eval kit (Fig. 2) start at $30. In incorporates an Arduino header. It includes a 10M08 MAX 10 with 8000 LEs.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: