Storage Visions is a trade show that occurs just before the Consumer Electronics Show in Las Vegas. Unfortunately I got to Las Vegas a little late (see “CES 2016: Getting There Is Half the Battle” on electronicdesign.com), but I did get a chance to check out the presentations and talk to some of the people that were at the show to find out what the latest storage trends are.

Storage Security

Security is not just topping the discussion for the Internet of Things (IoT). It was front and center in the discussions at Storage Visions. Jon Tanguy, Senior Technical Marketing Engineer at Micron (see Micron on sourceesb.com), noted that less than 10% of Crucial solid state disk (SSD) storage users used encryption features and most OEM customers want the Trusted Computing Group (TCG) Storage Workgroup’s Opal Storage Specification or eDrive features disabled by default.

There is also the rapid migration to SSDs from the enterprise on down to IoT devices. SSD characteristics make features like sanitized erase more important (Fig. 1). It also means that standards like NVMe (see “What's The Difference Between SATA And NVMe?” on electronicdesign.com) need to be, and are, being incorporated into encryption standards.

Of course, part of the discussion on self-encrypting drives (SED) is being driven by the Drive Trust Alliance (DTA). DTA was created to promote awareness and adoption of SED technology in the consumer market. It also helps for those in the enterprise and embedded sectors, although much of the drive for SED was initially from the enterprise. The challenge is there is a significant amount of education that must take place in the consumer and embedded markets.

NVM Programming Model

Non-volatile storage has typically not been part of the main memory discussion since the disappearance of core memory (see “Magnetic Cores To MRAM: Nonvolatile Tipping Point?” on electronicdesign.com) like this array from an old Burroughs 5500 I used to work on (Fig. 2). In those days it was more common for a system to boot and check the contents of memory to see if was still valid so it could be used immediately instead of being downloaded from disk or drum storage.

The non-volatile memory (NVM) programming model is something that is available now for microcontrollers from Texas Instruments (TI) with their MSP430 FRAM series (see “Microcontroller Utilizes FRAM For Code And Data” on electronicdesign.com and MSP430 FRAM on sourceesb.com). Code and data storage are non-volatile FRAM that runs at processor speeds. FRAM and other NVM technologies like MRAM are available (see “High-Density Storage” on electronicdesign.com).

TI’s FRAM is different than the current crop of NVM for microprocessors because FRAM essentially replaced flash and RAM storage in the microcontrollers. Most NVM solutions for microprocessors are either flash-backed DRAM like Viking Technology’s ArxCis-NV (see “Non-Volatile DIMMs and NVMe Spice Up The Flash Memory Summit” on electronicdesign.com and Viking Technology on sourceesb.com) or slower but higher capacity flash-only DIMMs like Diablo Technologies’ Memory Channel Storage (see “Memory Channel Flash Storage Provides Fast RAM Mirroring” on electronicdesign.com).

The former provides the same speeds for data and code as FRAM does on a microcontroller, but the NVM operation is handled by copying data between flash and DRAM at startup and shutdown with supercaps or batteries used to guarantee saving data when a system is powered down either intentionally or not. Flash-only storage tends to be used only for data, although code could be executed directly and more slowly or copied to DRAM. Both approaches use DIMMs that plug into the microprocessor’s memory channel, providing the fastest interface available for NVM. Intel’s new 3D Xpoint memory will eventually be found on the memory channel (see “3D XPoint: A New Revolution in Memory?” on electronicdesign.com).

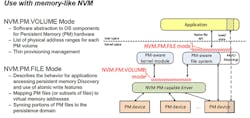

The Storage Networking Industry Alliance (SNIA) NVM programming model v1.1 is now out. It is not an API, but a model (Fig. 3). It exposes new block and file features with atomic operations along with thin provisioning management as well as how to use persistent memory mapped files. It includes an open-source implementation.

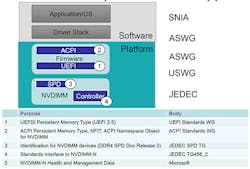

Microsoft is addressing NVM storage with a new Storage Class Memory (SCM) model (Fig. 4). Its Direct Access Storage (DAS) mode can use memory mapped files and cached IO. It will be supported by ReFS and NTFS file systems, although there will be some limitations like no NTFS encryption or compression.

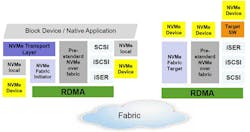

Mellanox looks to push persistent memory (PM) across networks and fabrics or NVM over fabrics (NVMf). It might be the killer app for RDMA (remote direct access memory). NVMf would use RDMA implmentations like InfiniBand, RoCE, or iSER (Fig. 5). The approach was first demonstrated at the NAB Show last year running at 10 Gbyte/s and 8 Gbytes/s reads and writes as well as 2.5 M random 4 Kbyte read IOPS using RoCE and InfiniBand. The approach allows hyper-convergence by collapsing separated compute and storage.

NAND Flash Continues to Dominate

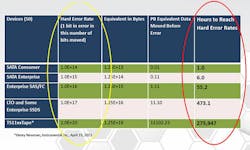

Don’t be too worried about flash disappearing any time soon. Samsung’s forecast (Fig. 6) shows major growth, especially as everyone moves from hard drives to SSDs and the cloud continues to grow in size--which means even more storage requirements. Samsung is addressing this growth with their V-NAND technology (see “The Changing Face Of Non-Volatile Storage” on electronicdesign.com). Samsung's V-NAND-based SM951 M.2 module stores up to 512 Gbytes (see “What’s the Difference Between M.2 Modules?” on electronicdesign.com). The M.2 modules mount directly on the motherboard. The modules employ a 48-layer stacked approach.

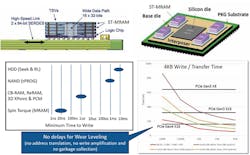

Not to be outdone, Terry Hulett, vice president, Systems Engineering and GM Systems Solutions Group for Everspin, noted that the company’s M-RAM technology is going 3D as well. It will use its ST-RAM (Fig. 7). M-RAM does have advantages, including a faster write time and no need for wear leveling. It is still not as fast as DRAM, but it is better than even Intel’s new 3D Xpoint technology. At this point, M-RAM has found use in file and disk servers. Everspin was also showing a PCI Express Gen 3 board with a NVMe 1.1 interface. It saturates a x8 lane interface and delivers over 1.2 M IOPS.

There are still no firm details on Intel’s Xpoint, although it is supposed to be 1,000 times faster with 1,000 times the endurance of NAND. It is also supposed to be 10 times denser. We shall see once Xpoint hits the market.

Other news from Storage Visions: the SCSI Trade Association anticipates a plugfest for 24 Gbit/s SAS in 2018. That is double the 12 Gbit/s available now.

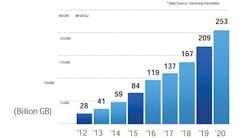

Fujifilm and IBM highlighted their support for barium ferrite (BaFe) tape. This past year they demonstrated 123 Gbpsi that translates into a 220 Tbyte tape module. Unlike conventional magnetic technology (tape or disk), BaFe appears to have a very long archival life in excess of 30 years. LTO-7 has a 6 Tbyte capacity (15 Tbyte compressed) with a 300 Mbyte/s transfer rate. It also comes down to reliability where tape excels (Fig. 8).

I’ll save the cloud and video storage discussion for a later date. That’s it for Storage Visions, for now.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.