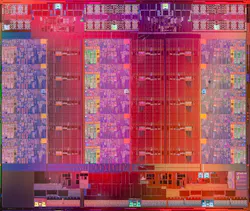

Intel's Xeon E7 v2 family (Fig. 1) pushes the top end platform even higher. It is built to live in 32-socket servers. The top end chips have up to 15 processor cores running at 3.4 GHz supporting 30 threads and up to 1.5 Tbytes of memory. It doubles the performance of the initial crop of Xeon E7 products. It gets some of this boost by increasing the number of cores by 50% and increasing cache by 25%. The memory controllers can also switch between lockstep for critical application and performance mode.

Related Articles

- AMD ARMs 64-Bit Servers

- 8-Core Chip To Dominate Server Market

- 8-Core Atom Expands Intel’s Server Strategy

- Intel and AMD Micros Target Enterprise And Cloud Servers

Large amounts of memory are key to applications like in-memory analytics. A 32-chip solution would have access to 48 Tbytes of memory. These large solutions require third party interconnect support. The processors have three Quick Path Interconnect (QPI) allowing multichip 2S (socket), 4S and 8S solutions without requiring additional interconnect hardware. The QPI links in the Xeon E7 v2 family run at 8 Gtransactions/s.

The latest crop of processors utilize 128 PCI Express Gen 3 lanes. This provides up to four times the bandwidth of the PCI Express Gen 2-based chips.

Intel's Run Sure technology is designed to increase reliability to 5 nines (99.999%). It includes support for PCIe Live Error Recover (LER). LER helps contain PCI Express errors that would cause a system to crash. The Machine Check Architecture (MCA) Recover Execution Path allows error recovery from potentially fatal errors. This also includes generation of enhanced error log information that can be used for diagnostics and predictive failure analysis.

If you think 48 Tbytes and lots of cores is big then consider that eBay has data sets on the order of 50 petabytes for their millions of users. Other applications are equally memory and performance hungry. The top end chips utilize 155 W and have 37.5 Mbytes of L3 cache. All support Intel's HT (hyperthreading) technology and Turbo Boost technology.

Although clearly targeted at the enterprise and HPC market, the Xeon processor has been increasing used in the embedded space where heavy duty computation is required. This include military application.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: