64-bit MIPS Architecture Targets High Performance Designs

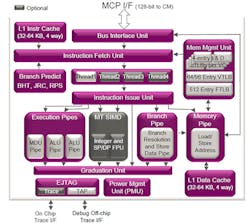

Imagination Technologies latest 64-bit processor architecture targets high performance mobile applications. The Warrior Class I6400 (see the figure) is Imagination’s mid-range offering. It supports simultaneous multithreading (SMT) that allow the system to execute multiple instructions from multiple threads. Each core can run four threads. A quad core system can fit on 1 mm by 1 mm space running at over 1 GHz.

The system uses a new directory-based coherent cache manager. Other system typically use a snooping approach. The L1 cache is mirrored in L2 allowing more system flexibility since all cores can operate independently including operating at different speeds. ECC is used with all caches. Hardware prefetch reduces memory latency overhead.

The core is designed to be used in coherent clusters with up to six cores. The architecture supports 64 clusters for a total of 1536 threads. The design supports AXI4/ACE system interfaces.

The I6400 runs 32-bit and 64-bit instruction sets. The 64-bit instruction set is a proper superset of the 32-bit version so there is no mode switch necessary. The additional instructions support 64-bit data types along longer relative referencing.

The system includes a 128-bit SIMD unit. The RISC-based unit has a symmetrical, orthogonal design. The instruction set is independent of register width and they support compare and branch instructions. It has 32 128-bit registers. The architecture is designed to support high level parallel programming platforms like OpenCL.

Hardware virtualization support includes virtualized interrupt controller support as well as I/O virtualization.

The PowerGearing power management provides fine grained, block- and core-level clock gating. Each core in the cluster is independently controlled including the ability to sleep. Dynamic voltage and frequency scaling is supported.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: