Performance, Power, and Security Top Digital Hardware Trends

This file type includes high resolution graphics and schematics when applicable.

Smaller, faster, and lower power remain the mantras for digital technology this year, but security has been added to the list primarily driven by the phenomenal growth of the Internet of Things (IoT). At least the increased connectivity due to IoT designs and the never-ending reports of security breaches, buggy code, and cyber attacks has pushed the design and development community to bring security to the forefront.

Expect the usual churn in 8-, 16-, 32-, and 64-bit microcontrollers and microprocessors with interesting multicore combinations and ties to GPUs as well as specialized controllers for handling real-time and communication chores.

Storage is about DDR4 and the plethora of flash memory systems that will effectively push hard-disk storage to the sidelines for the majority of applications.

Now for a few specifics:

Hardware Security for the Internet of Things

Hardware-based security support is not new, but the number of chips that have it is rapidly increasing. ARM’s 2015 announcement of the ARMv8-M architecture. The low-overhead, ARMv8-M specification adds TrustZone support to the 32-bit Cortex-M microcontroller series. The Cortex-M architecture enjoys the widest 32-bit support in the microcontroller space.

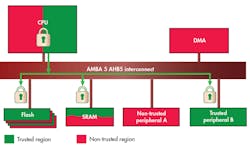

TrustZone support was already available for the Cortex-A family. The two implementations are not identical as the ARMv8-M definition needed to address the real-time needs of the Cortex-M microcontrollers. The ARMv8-M provides an untrusted user and trusted system mode of isolation that also partitions memory and peripheral access (Fig. 1).

ARMv8-M also includes architectural enhancements such as hardware divide, compare and branch instructions, and long branching for cross-unit tail-call support. It is also designed to handle multiprocessor system support with the addition of C11 atomic data-type instructions.

Other security-related support that is becoming more prevalent is anti-tamper support. This is needed for protecting user data as well as protecting intellectual property (IP) in the form of applications and algorithms. Again, this is not a new idea but one that is becoming more standard and less expensive.

High-Performance Computing

Dozens of 64-bit CPU cores and even more GPU cores on a single chip will be the norm as densities increase and chip-process resolution decreases. ARM’s 64-bit cores are becoming more popular in the enterprise, complementing the increased performance already used in the mobile space. The ARM Cortex-A72 provides more performance than the current crop of Cortex-A5x chips, but at this point Intel remains the leader in processor architectures. Intel is expected to deliver Broadwell-based Xeons with up to 24 cores.

The Intel Xeon Phi (Fig. 2) will be getting a major refresh. The ring architecture will be replaced with a mesh used in competing many core devices. The Knights Landing implementation will be built around two Silvermont cores. The 16 Gbytes of in-package, multi-channel DRAM (MCDRAM) will challenge AMD’s high-bandwidth memory (HBM) implementation found in its current crop of GPU boards.

The new Xeon Phis also use Intel’s Omni-Path Architecture. A four-lane connection operates at 25 Gbits/s. It is designed for low latency. Copper and optical connections can be utilized between chips and boards.

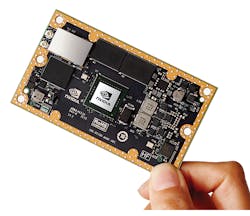

AMD and NVidia’s GPUs will remain an important HPC component in addition to providing graphics support. NVidia’s Maxwell architecture is in the latest GTX 970 boards. The NVidia Tegra X1 on the Jetson TX1 module has four, 64-bit ARM Cortex-A57 cores plus 1024-GFLOP Maxwell GPU with 256 cores (Fig. 3).

Pushing Communication Limits

The USB 3.1 Type-C connection will be the communication darling this year. It has the bandwidth and is reversible, making it more convenient and easier to use . It also supports a more advanced power-management system that can deliver significantly more power than the prior USB standards.

The Type-C cabling also supports different protocols, not just USB. This is an advantage and can allow a system to have a single connector to handle different types of connections such as DisplayPort, but this feature could be confusing to users. Add this to the higher cost of Type-C cables because they must incorporate at least some electronics for handshaking and there is the potential for user confusion.

Many IoT devices will sport a Type-C connector, but wireless tends to be the choice for mobile devices. 4G is obviously part of the smartphone and many tablets that are likely to include near-field communication (NFC) support. NFC will primarily be used for electronic payment systems, but more creative pairings are possible as well.

Developers and consumers will have to contend with Bluetooth Smart/Bluetooth Low Energy (BLE) as well as legacy Bluetooth. BLE delivers significant advantages from much lower latency and power requirements to better device handling.

Zigbee and Z-Wave continue to improve, but IoT software standards like Thread from The Thread Group that uses 6LoWPAN will be making the 802.15.4 space more interesting.

Another IoT interface to keep an eye on comes from the LoRa Alliance. LoRaWAN is a Low-Power Wide-Area Network (LPWAN) specification designed for wireless battery-operated devices. It operates at low bit rates (under 100 Kbits/s) in the ISM bands, but the radios can operate over long distances over 100 km.

The current 4G environment will provide IoT support from a cellular standpoint, but it will be worth watching the emerging 5G standard. Ken Karnofsky, senior strategist at MathWorks, says, “Heading into 2016, we’re seeing a significant increase in customer interest and activity in the area of 5G research.”

Designers will be able to take advantage of more multiprotocol solutions such as chips that support WiFi, Bluetooth, and 802.15.4.

Storage Wars

Flash memory technology is a confusing hierarchy of chip technologies and packaging ranging from eMMC chips to NVMe-based drives. The DRAM landscape tends to be less confusing with DDR3 and DDR4 dominating and new motherboards pushing the DDR4 bandwidth.

The non-volatile RAM (NV-RAM) space is heating up. Diablo Technologies Memory1 puts 1 Tbyte of flash into a single DIMM socket on the processor's memory channel.

Flash memory is available in m.2 (Fig. 4) and conventional-drive form factors using SATA, SAS, and PCI Express (PCIe) interfaces, with PCIe having the edge on throughput. The m.2 is also finding a home of motherboards allowing very compact system designs.

Samsung started the 3D race with its V-NAND. This is just one of many stack storage systems that will be readily available this year. AMD’s HBM chip architecture is another. It brings stacked DRAM into the same package as AMD’s GPU.

This year will also see more flash memory alternatives turning into real products. Texas Instruments is already using FRAM in a range of its MSP430 microcontrollers. According to Jim Handy, an analyst at Objective Analysis, Intel’s new 3D XPoint memory technology fills a gap between DRAM and flash storage. Intel is still keeping quiet about the details about the technology, but it will eventually show up in areas where flash is used now (including on the memory channels like Memory1).

Server and enterprise systems may have a steep memory hierarchy with various nonvolatile memory technologies delivering different levels of performance and cost. The hierarchy starts at the memory channel where DRAM and flash can reside.

SWaP+C Drives Military Technology

Mergers and acquisitions in this space have made 2015 interesting, but military technology continues to push the envelope. ARM-based systems are becoming more prevalent with Intel platforms dominating in many areas.

John Cowles, general manager, RF and Microwave Group at Analog Devices, notes, “Advanced defense systems are pushing the boundaries of performance even as they continue to reduce size, weight, and power (SWaP). In addition, the demand for multifunction systems and the need to reduce system development costs (SWaP+C) is driving system designs to be more modular and platform-centric, further pushing semiconductor integration levels and device configurability. Advanced SiGe, CMOS, and GaN technologies are well aligned with these goals, providing higher levels of integration, the inclusion of digital signal processing, and improved efficiency.”

High-end FPGAs with very fast SERDES will provide more performance typically through the use of advanced chip packaging that allows multiple chip technologies to be combined into a single package. High-speed, rugged systems communications will continue to use 10 G and 40 G Ethernet.

This file type includes high resolution graphics and schematics when applicable.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: