This article is part of TechXchange: RISC V

Download this article in .PDF format

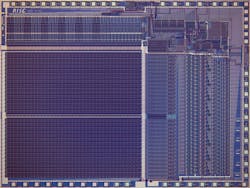

RISC-V (RISC five) is a compact, open-source, instruction-set architecture (ISA) that is ideal for embedded applications, including low-power platforms for the Internet of Things (IoT). It was originally developed at the Computer Science Division of the EECS Department at the University of California, Berkeley (see figure) and it has its own foundation to foster its use and adoption.

The RISC-V was developed at Computer Science Division of the EECS Department at the University of California, Berkeley. This die shot is of the original RICV-I chip.

RISC-V is a true reduced instruction-set computing (RISC) platform using an explicit load/store architecture. The ISA uses 32-bit instructions and it does not have condition codes, using register-based comparison branching instructions instead. It is based around a register file with 32 registers, although register 0 contains a value of zero. The system can be configured with 16-, 32-, 64-, and 128-bit registers. There is no hardware stack. The jump and link (JAL) instruction copies the program counter to a register. A software stack is generally implemented when needed. The advantage is that different stack implementations are possible.

The RISC-V implementation designations include a number of instruction extensions denoted by letters.

- I–base integer configuration

- E–embedded version with only 16 register file

- A–atomic, real-time instructions

- C–compact 16-bit instruction set for embedded applications

- M–integer multiplication and division

- F–single precision floating point

- D–double precision floating point

- Q–quad precision floating point

- G–general, includes IAFDP

There are additional extensions for features like SIMD support. A typical embedded instantiation would be designated RV32EC (RISC-V, 32-bit, 16 register file, compact instruction set). High-end implementations of RISC-V can run operating systems such as Linux.

RISC-V is ideal for embedded applications. The base system has less than 50 instructions. This enables additional instructions to be added even when features like floating point are included. RISC-V is supported by compiler technologies like GCC and LLVM that can handle additional instructions. Low-power IoT applications can benefit from this approach by implementing some functions in hardware.

RISC-V started as an academic exercise, but has moved into the commercial space courtesy of companies like SiFive. SiFive’s Freedom series are actual RISC-V core implementations. The Freedom U500 platform is a RV64GC implementation, while the Freedom E500 is a RV32IMC/RV32EMC implementation. The U500 is available through TSMC using its 28-nm technology. It includes support for multicore implementations with cache coherency and support for high-speed peripherals, including PCIe 3.0, USB3.0, Gigatbit Ethernet, and DDR3/4 memory controllers. The E500 uses 180-nm technology support on-chip flash memory, OTP, and SRAM.

Those not wanting to dive into a custom chip can take advantage of Microsemi’s SmartFusion 2 FPGAs that support RISC-V. Microsemi supports a range of RISC-V implementations up to the 128-bit RV128I. Microsemi's FPGAs support ARM’s Cortex-M1 but this would need to be licensed if a design were to move from FPGA to a custom ASIC. That would not be the case with RISC-V. Microsemi includes a complete development platform with its Libero FGPA IDE and the Eclipse-based SoftConsole software IDE. The system includes graphical configuration tools.

RISC-V’s simplicity can also be advantageous in safety and security applications that require certification. Of course, ARM already does this for some of its platforms.

(By the way, this article title is a revamped version of a quote from the movie Short Circuit. Number 5 is the robotic central character. )

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: