Special Report: PAM4, PCIe, jitter limits move the needle in high-speed digital

While high-speed digital design engineers continuously combat demands for products and systems that are lower power, lower cost, more reliable, user-friendly, mobile, and faster than ever, test engineers are challenged to determine if shown defects are rooted in the design, or in the equipment being used to test them.

Being a good test engineer means taking the proper steps to ensure errors caused by things such as bad connections, worn-out cables, and human error are systematically eliminated. It also means ensuring uncertainties caused by test equipment are accounted for.

Tight budgets may make ‘just good enough’ equipment appealing to test engineers, but that increases the likelihood of illegitimate test results. Thus, these engineers are also tasked with keeping up with the latest developments in high-speed digital test equipment and using cutting-edge instruments that keep up with the pace of technological developments.

Trending

Data rates will only speed up in 2019, with that key factor leading trends in high-speed digital test. We at Evaluation Engineering asked a number of test equipment vendors about what they’re seeing as trends in this space. Here’s what they had to say.

Faride Akretch, marketing manager for Rohde & Schwarz: “There are several trends that we see, and they are all related to the increasing speed of clocks and data and all have different implications on how to test. First, as the data rates in high-speed digital designs increase, the limits for overall system jitter become tighter. This especially applies to the various components of the clock tree, where the jitter limits for reference clocks, clock buffers, and jitter attenuators are even tighter. Here, the trend is to increasingly use phase noise analyzers. Second, in regard to the signal-integrity aspect of high-speed digital designs and the components used, vector network analyzers (VNA) are increasingly replacing traditional time domain reflectometry (TDR) setups for testing passive components such as connectors, cables, and PCBs. Users benefit from the higher accuracy, speed, and ESD robustness of the VNA, making the VNA the instrument of choice in this field. And thirdly, with more and more radios, components, and complex sub-systems all part of a design, we do see a trend towards multiport instruments, where many interdependencies can be tested at once.”

Keyur Diwan, group product marketing manager for Tektronix: “To keep pace with data center communication needs at 400G and enable new applications, the PCIe 5.0 specification is in development, which will increase throughput to 32 GT/s, while also meeting more demanding requirements for low latency and power efficiency. Other trends include:

- The shift to cloud services is driving the need for ever larger networks for the cloud providers. 400Gb/s for DCI and metro networks will soon be commercially available.

- Coming technology transitions of >400G/600G will drive new technologies to overcome current physical limitations of direct detect links. The new standard for baud rates >400G is 400G ZR –coherent modulation is getting a lot of traction.

Brig Asay, director of strategic planning—Internet Infrastructure Group, at Keysight Technologies: “We expect that 2019 will be the year of the fifth generation as PCIExpress, and DDR will both be rolling into their fifth-generation technologies. As PCIExpress moves to Gen5, its recent competitors—CCIX, GenZ, OPENCapi, etc.—will all need to gain market share and show their value to stay in consideration. It is no longer viable from them to just be >30 Gbps, but they must show that they have value outside of speed alone. We expect that virtual reality and augmented reality will continue to gain traction, pushing display technologies to new generations. We also see the beginning of the convergence of buses that are using type-C connectors such as USB and DisplayPort.”

Patrick Connally, product manager at Teledyne LeCroy: “The electronics industry’s ongoing shift to the next generation of high-speed communication buses (such as PCIe Gen5) gives rise to the challenges of sending faster signals over relatively lossy channels. As 2019 approaches, current high-speed specifications are looking to double their speed or bandwidth while also trying to reduce power consumption. This, in turn, makes design margins smaller and test requirements more complex. This trend manifests in communications standards through requirements such as dynamic link training, in which the interactions between the physical and protocol layers become increasingly important.

The drive for lower power consumption in many devices and systems means lower power-rail voltages, which in turn means that those rails can tolerate very little noise before they infringe on high-speed data transmission. Thus, power-integrity (PI) analysis is of increasing importance in high-speed systems.”

Hiroshi Goto, business development manager at Anritsu: “Data traffic volumes are expected to increase due to the spread of next-generation 5G mobile communications and cloud services. To cope with this demand, infrastructure operators, such as data centers, are investigating not only speed increases, but also PAM4 and multilane communications methods. 400GbE speeds are being deployed using either the 26.5625-Gbaud PAM4 x 8 lanes or 53.125- Gbaud PAM4 x 4 lanes methods. When using the PAM4 method expressing data as four amplitude levels, the gap between signal levels is one-third that of the NRZ method, which reduces the unit time per symbol at higher baud rates, emphasizing the importance of signal quality in achieving high-speed transmissions. On the other hand, the inability to avoid degraded signal quality caused by crosstalk and noise resulting from use of multiple lanes and high-density circuit design increases the need for evaluation of minimum Rx sensitivity using stress-test signals.”

At DesignCon

These trends and the vendors providing high-speed digital test equipment will be on display at DesignCon, held Jan. 29-31 in Santa Clara, CA. Now in its 24th year, DesignCon brings together nearly 5,000 professionals in the high-speed communications and semiconductor communities for three days of education and networking activities, and brands itself as the largest U.S. event for chip, board, and system designers.

Rohde & Schwarz will be on-hand at DesignCon to feature their latest VNA, phase noise analyzer, and oscilloscope solutions for signal integrity measurements. These solutions cover specifications including high-frequency multiport crosstalk—which the company promotes as the first multiport VNA offering up to 24 integrated test ports—PAM4, PCIe clock jitter, de-embedding, and high-speed PCB probing. Power rail probes will also be in the Rohde & Schwarz booth, displaying power integrity measurements. Rohde & Schwarz will also run a series of seminars on de-embedding, signal integrity, power integrity, power rail sequencing probing, clock jitter measurements, characterization of signal integrity using VNAs, and crosstalk.

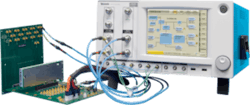

At booth No. 615, Anritsu will debut its 64-Gbaud PAM4 Pulse Pattern Generator (PPG) and 32-Gbaud PAM4 Error Detector (ED) modules, supporting 400GbE and Over 400G bit error rate (BER) tests for its Signal Quality Analyzer-R MP1900A BERT. Anritsu said with the modules installed, the MP1900A provides engineers with best-in-class signal quality and excellent Rx sensitivity to more accurately verify performance of 400GbE optical modules and devices being designed for high-speed communications systems.

Asay said Keysight plans to show it is up-to-date in the latest trends in VNA/PCE solutions and DDR, while also showing it is future-ready by demonstrating its latest real-time oscilloscope introduction and its 110 GHz of bandwidth. “We will demonstrate the merging of customer workflows and the need for data that can be compared from design/simulation through validation through manufacturing with our DDR4 software solution, which fully merges our validation software with our simulation software,” Asay said, adding that Keysight will show its expertise in 400GbE with both Tx and Rx solution demonstrations.

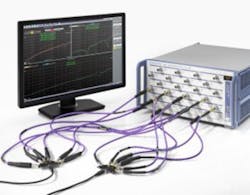

The folks at Teledyne LeCroy will exhibit a new test solution for PCI Express Gen5 physical-layer transmitter and receiver testing. This solution centers on the company’s LabMaster 10 Zi-A oscilloscope and includes automated receiver test calibration for Anritsu’s MP1900A signal-quality analyzer. Also featured at DesignCon for Teledyne is its WavePro HD—an 8-GHz, 12-bit oscilloscope ideally suited to PI analysis, particularly when paired with Teledyne LeCroy’s RP4030 voltage-rail probe. In terms of protocol analyzers, the company will exhibit the Eclipse M42x Protocol Analyzer/Exerciser for universal flash storage and the Envision X84 Protocol Analyzer for MIPI C-PHY and D-PHY. Teledyne LeCroy will also showcase the Summit M5x PCIe Analyzer and Jammer, which is PCIe Gen5 capable. See it all at booth No. 519.

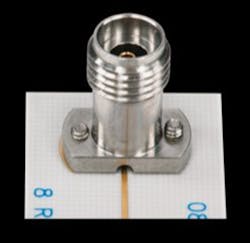

Signal Microwave, at DesignCon, will highlight a turnkey TRL/LRL calibration system for SMD testing, and a new 40 GHz top launch connector for easier board design and improved performance over current vertical launch connectors.

Tektronix’ booth at DesignCon will exhibit four solutions: its 400G PAM4 & Coherent Optical; the PCIe GEN 5 advances on the TEK BSX BERTScope Series; consumer-based USB & HDMI; and memory-based DDR 5 & LPDDR 5.

Solving challenges

Some of the key challenges that customers face in the design and test of high-speed serial interfaces have already been mentioned. We asked T&M equipment vendors about challenges their customers are taking on, and the solutions those vendors are providing to help.

Akretch, Rohde & Schwarz: “The R&S FSWP Phase Noise Analyzer and VCO Tester offers the functionality needed to test low-jitter clocks in both SSC OFF mode and SSC ON mode. It provides very high AM suppression in the phase noise measurement and excellent phase noise sensitivity for precise jitter measurements on low-jitter clocks for modern high-speed digital designs. For multiport measurements, The R&S ZNBT is the only true multiport vector network analyzer with up to 24 ports. It enables engineers to characterize crosstalk with a single connection, increase production throughput, and with an optimized user interface and multiport—get it done quickly. On the VNA side, and in comparison to traditional TDR solutions, the R&S ZNB Vector Network Analyzer offers all the functionality needed to test digital high-speed signal structures on PCBs in one box. Additional de-embedding tools can be installed on the instrument to remove the effects of probes, probe pads, vias, lead-ins, and lead-outs.”

Diwan, Tektronix: “One of the biggest challenges for customers is getting their devices into loopback to perform jitter tolerance test. This cuts across standards such as PCIE and USB. Validation teams aren’t always sure of how many packets of TSI, TSEQ they need to send device to get it into loopback. This leads to a time-consuming and difficult trial-and-error of configuring packets. BSX Series BERTScope solutions for both USB and PCIE provide built-in intelligence to send packets to the point when they have handshaking from the device and getting the device into loopback while eliminating trial-and-error.”

“Customers need to analyze electrical PAM-4 signals through backplanes—interconnects that are highly impaired—and advanced analysis tools are required to measure and debug PAM-4 modulated signals. Our Tektronix real-time scope solution (DPO-series) provides research & development with advanced tools such as digital clock recovery, visual trigger, BER analysis, and powerful CTLE to successfully measure PAM-4 signals—reliably and repeatably.”

“Tektronix solutions allow precision measurement SDLA tools for equalization and S-parameter loss de-embedding using the DPO70000SX oscilloscope, able to capture up to 70GHz signals with the lowest-noise and highest fidelity, as well as BER analysis. Tektronix DPO-series offers a comprehensive test and measurement solution addressing PAM4, NRZ & coherent optical & electrical signal analysis in a single instrument. The Tektronix BSX Series BERTScope bit error rate tester features customizable pattern sequencers and capture-and-decode triggering to gain insight into a problem’s root cause.”

Bill Rosas, president and CTO of Signal Microwave: “The test connector to PCB interface is difficult to design and fabricate. We supply 3D models of our connectors and reference designs for many common PCB materials. We also have reference test boards for customers to use to verify our connector performance. Our TRL/LRL is a tried-and-true alternative to de-embedding to remove the effect of connectors in device testing using calibration algorithms available in all common VNA systems. Our top launch connector helps solve the challenge of board design and fabrication to get 40 GHz bandwidth signals into and out of PCBs.”

Asay, Keysight: “Time-to-market is becoming king in today’s high-speed digital market. This is not news, but with every passing generation, it becomes more prevalent across the industry. Our customers are pressed to obtain solutions early and have confidence that testing is completed in a way, if it passes on a Keysight solution, it will pass on their customer DUTS. The solutions we will be showing at DesignCon illustrate Keysight’s commitment to being in the market early with full testing solutions and our commitment to ensure we fully test our customer’s devices. We have many Keysight fellow employees that stay up-to-date on the latest standards and ensure that our solutions match the latest standards movements. Our DDR5 solutions reflect not only do we test to the standard, but we are an active participant on the standard and ensure the testability of the standard.”

Connally, Teledyne LeCroy: “As the speeds of high-speed digital communications increase and power is reduced, the signal strengths and signal lengths are also reduced. This requires unique and delicate probing of the transmission signals to be able to record the transmission without disturbing the end-to-end signal. Teledyne LeCroy offers the widest array of probing solutions of any test and measurement company. In the new PCI Express Gen5 test solution mentioned above, we offer a platform that covers test for every generation of PCIe from 1 to 5. It also leverages the high-power computing platform in the LabMaster to dramatically reduce calibration and test times. The WavePro HD offers 8 GHz bandwidth, 12-bit vertical resolution for very low noise, and 5 Gpoints of acquisition memory to capture infrequent high-speed phenomena over long time scales. Like all of Teledyne LeCroy’s oscilloscopes, it also provides the industry’s deepest set of tools for waveform capture, viewing, measurement, math functions, analysis, and documentation.”

Goto, Anritsu: “Anritsu has developed the 64-Gbaud PAM4 PPG and 32-Gbaud PAM4 ED to support evaluation of equipment and devices using either the 26.5625-Gbaud PAM4 x 8 lanes or 53.125-Gbaud PAM4 x 4 lanes methods. The introduction of the MP1900A PAM4 modules addresses the market need for solutions that can accurately measure devices designed for high-speed, large-capacity transmissions such as those for 5G and cloud services.”

“The new PPG can output PAM4 signals up to 64 Gbaud and has the world’s best Tr/Tf of 8.5 ps and intrinsic jitter of 170 fs. It has a multichannel synchronize function that can expand up to four channels, and an emphasis function that corrects signals degraded by transmission path loss for more accurate measurement results. With high sensitivity performance of 23mV, the 32-Gbaud PAM4 ED module supports an embedded clock recovery function required for Rx jitter tolerance test, as well as PAM4 symbol error measurements.”

“Configured with the new modules, the Signal Quality Analyzer-R MP1900A can generate high-quality PAM4 signals. This best-in-class performance allows the true performance of 400GbE optical modules and devices to be tested with adequate margin to satisfy industry specifications for the first time.” EE

About the Author

Mike Hockett

Former Editor

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: