IBIS AMI Versus Spice: Which Is Best For Communications Simulation?

As communication speeds increase, engineers are challenged with ensuring their designs have an excellent chance of working before the printed-circuit board (PCB) assembly is built. Done through modeling, this can be extremely complex. In the world of communications, there are two competing solutions for modeling the behavior of these devices and the channels they drive.

First there’s Spice, the de facto standard supported by much of the world’s simulators. Second, there’s a newcomer, Input-Output Buffer Information Specification (IBIS) algorithmic model application program interface models, which extend IBIS including analog modeling of inputs and outputs.

Background

Since the dawn of the electronics industry, engineers have used mathematics to calculate circuit behavior in both the time and frequency domains. These solutions required complicated and error-prone calculations, along with the necessary time to complete them. With the advent of the modern computer, engineers began to write software to handle these calculations and remove the potential for human error.

In the 1960s, the Department of Defense (DOD) was issuing contracts to create software to simulate the radiation hardness of circuits. The politics of the time led to the development of non-DOD simulators such as the computer analysis of nonlinear circuits, excluding radiation, or CANCER. This simulator was developed at the University of California, Berkeley, by Professor Ronald Rohrer and his graduate students, including Laurence Nagel. Rohrer’s successor convinced Nagel to rewrite the CANCER program to remove the proprietary information and release the new simulator into the public domain.

Spice Is Born

In 1973, Nagel presented his Simulation Program with Integrated Circuit Emphasis (Spice) at a conference. But due to limitations, it wasn’t widely accepted until SPICE2 was introduced in 1975. These early versions were written in FORTRAN. Thomas Quarles rewrote it in C in 1983 under the guidance of the dean of Berkeley’s college of engineering, Arthur Richard Newton.

This new version kept the same syntax as its predecessors and added support for the graphical X Windows system. It was an “open-source” simulator and was released into the public domain, leading to many of the modern commercial and non-commercial simulators based on the Spice syntax.

Spice simulations can include proprietary information since they represent the actual circuit being simulated. They are excellent for simulating the performance of circuits, but they can take a large amount of computational time when there are extremely large numbers of transistors in the circuit.

This is also a problem when modeling system characteristics such as the bit-error rate (BER) of communications channels where the simulation must run long enough to include large bit run lengths (potentially millions of bits). In the early 1980s, Intel detailed IBIS as a means to simulate board-level systems without exposing proprietary information and to reduce the amount of time the simulation would run.

IBIS modeling

IBIS models are behavioral—that is, they define the behavior of a buffer’s analog circuitry without revealing how the circuit is implemented. They allow vendors (producers of ICs and electronic design automation tools) and system engineers to exchange human-readable information on digital devices for analog simulations of interconnects.

IBIS models use I-V tables to define the output drive of the buffer, V-t tables to describe the rate of change of the output, and capacitance information for simulating the driver’s impedance. If this information is provided over temperature, voltage, and process variation, a very accurate simulation of the buffer’s behavior can be achieved.

These models work extremely well on simple drivers or buffers and can simulate best, typical, and worst case scenarios. IBIS models also include package parasitic Ls and Cs, which provide the ability to simulate simultaneous switching outputs.

However, the basic IBIS models through version 4.0 cannot simulate advanced drivers with complex output behavior, such as self-tuning terminations. An extension was made in IBISv4.1 and 4.2 to use a hybrid approach that kept all the good things about IBIS such as pin lists, package information, signal names, input thresholds, and output delays, but replaced the buffer definition with a more advanced analog (and optional digital HDL) representation.

In IBISv5.0, this concept was extended to include a technology called Algorithmic Modeling Interface (AMI), which allows the modeling of drivers with de-emphasis or pre-emphasis and even receivers that implement equalization to compensate for channel loss. This is accomplished by adding compiled code in the form of a dynamic link library (DNN) to the model via an application programming interface (API) that describes the extended behavior.

With the addition of advanced processing found in modern buffer-repeaters, re-timers, and serializer/deserializers (SERDES), this addition now enables advanced signal integrity simulation for complex systems. This is a must have when speeds now routinely reach and exceed 8 Gbits/s, such as in PCI Express and 10G Ethernet.

IBIS AMI models provide both impulse and continuous waveform simulations and can be chained together to provide a complete transceiver/receiver (TX/RX) channel. In the impulse response mode, the impulse data is supplied to the model, which applies its processing such as pre-emphasis to the data. It then returns the modified data to the simulator.

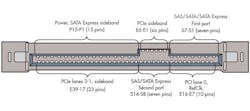

This data can be used to statistically simulate long runs of data and create eye-patterns or bathtub curves as well as extrapolate BER information. The same process applies to the continuous time-domain mode, which also passes the time-domain waveform to the model which then processes the data (for example, with equalization, etc.) and returns it to the simulator. This method allows vendors to include complex behaviors not easily modeled without disclosing how it was implemented, as in the Spice dilemma (see the figure).

Both IBIS AMI modes have advantages and disadvantages when simulating high-performance channels. The impulse mode provides extremely fast modeling since the result is directly calculated from the impulse response data, so a large statistical range can be examined. This provides a method to study issues that would occur over large run lengths (for example, 2^32 bits), which otherwise would be impractical to simulate with continuous wave data.

On the other hand, the continuous waveform data provides more detail on the behavior of the channel. As mentioned previously, IBIS models are extremely fast relative to Spice models, so running million-bit simulations is actually practical. However, this mode of simulation is often used to observe the behavior of specific patterns or to examine the time an equalizer would require to reach an optimum value.

Conclusion

It may be obvious at this point, but our IBIS AMI versus Spice throw-down favored IBIS AMI for modeling the latest complex high-speed interconnects. It hides the proprietary nature of the interface components, provides both an impulse and continuous-time mode of operation, and can simulate complex functions such as de-emphasis, equalization, clock recovery, and BERs without running your simulations for a thousand years.

With channel bit rates increasing beyond 10 Gbits/s, simulation will no longer be an option. With IBIS AMI modeling, all of the complexity can be studied before a single transmission line is etched into copper.

Richard Zarr

is a technologist at Texas Instruments focused on high-speed signal and data path technology. He has more than 30 years of practical engineering experience and has published numerous papers and articles worldwide. He is a member of the IEEE and holds a BSEE from the University of South Florida as well as several patents in LED lighting and cryptography.

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: