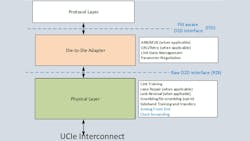

The UCIe Consortium’s Universal Chiplet Interconnect Express (UCIe) specification is in its second iteration. It targets designs built around chiplets providing the interconnect between die. The die-to-die standard defines a complete stack from the physical layer on up (Fig. 1).

UCIe has quite a following, including Synopsys, which provides IP as well as design tools that support UCIe. I talked with Mick Posner, Vice President of Product Management at Synopsys, about UCIe and what it involves from design to testing (watch the video above).

UCIe supports a multi-vendor ecosystem for system-on-chip (SoC) designs using chiplets. It complements other die-to-die interconnects like the Open Compute Project’s bunch-of-wires (BOW) specification.

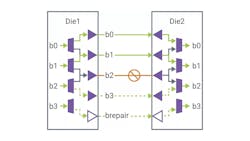

The UCIe 2.0 specification added features like optional manageability and the UCIe DFx Architecture (UDA). It defines a management fabric within each chiplet to support telemetry, testing, and debug services to provide a unified approach to chip management. The new specification is backward compatible with features like spare link, which allows for continued operation when another link fails (Fig. 2).

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.