Examining Cadence’s Physical AI Chiplet Platform

What you'll learn:

- What is physical AI?

- What is included in Cadence’s Physical AI Chiplet Platform?

- What is the Chiplet Spec-to-Packaged Parts ecosystem?

Physical AI takes advantage of the improvements in artificial intelligence (AI), including chatbots and large language models (LLMs), which incorporate hardware and software advances to address advanced robotic solutions such as cobots. These days, robots wandering around supermarkets are commonplace, but they tend to be silent, rolling autonomous mobile robots (AMRs). AMRs are also popping up in warehouses and hospitals.

The move to physical AI provides more interactive robots with a better understanding of their environment and how they can work with people. However, that requires more advanced hardware and software to handle human interaction. Using the cloud is one option, but it really requires AI on the edge.

Low-power, high-performance computing (HPC) is needed to get that level of AI capability. That means high-performance chips, which is where chiplets comes into play. Chiplets are already heavily utilized in cloud-based AI.

Physical AI Chiplet Platform

In the video above, I talk with Michael Posner, Group Director at Cadence, about the company’s Physical AI Chiplet Platform that’s part of its Chiplet Spec-to-Packaged Parts ecosystem. Ecosystem partners include Arm, Arteris, eMemory, M31 Technology, proteanTecs, Silicon Creations, and Trilinear Technologies. The chiplet platform provides pre-integrated solutions to developers of chiplet-based packages.

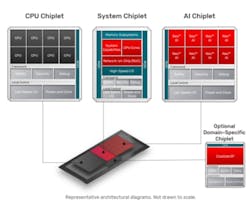

Michael highlighted the TC1 chiplet demonstration hardware that features a number of UCIe-connected chips sharing data via AXI-based memory interfaces (Fig. 1). The design tools and IP allow developers to utilize existing designs with connectivity to other chiplets employing standard interfaces like UCIe. The use of AI-based chiplet solutions along with supporting memory options like high bandwidth memory (HBM) let designers quickly integrate hardware needed to support physical AI models in the field.

The TC1 platform implements four chiplets (Fig. 2). This basic infrastructure can be customized and extended to provide additional AI, compute, and storage capabilities. Chiplet-based solutions like NVIDIA’s Blackwell also incorporate chiplets like HBM storage.

>>Check out more of our 2026 Chiplet Summit coverage

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.