New LoRaWAN Chips Designed to Handle Dense Networks

New wireless network chips seem to be cropping up all over the place. Sigma Designs’ 700-Series chipset increases range and uses less power. A sensor can run on a coin-cell for 10 years, even with the built-in ARM Cortex-M processor.

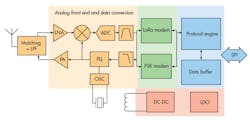

Semtech’s new SX126x family (see figure) targets LoRaWAN, a low-power, low-speed network with long range. LoRaWAN targets applications like smart meters, asset tracking, healthcare, and street lighting, where the technology’s advantages and limitations match the wireless requirements of the systems. LoRaWAN devices can be very simple, as are the gateways, with much of the routing management being done at a higher level that may be in the cloud.

The chip family reduce power requirements, increases range, and supports the new SF5 spreading factor designed to handle dense networks. SF5 uses less spreading, allowing faster speeds and short connection times while providing a better connection.

The chips can use 50% less power in receive mode. They can also extend the range of communication by 20% compared to the prior generation. They have a transmit power of +22 dBm. The chips support Class A that is optimized for power consumption, as well as Class B and always-on Class C. The chips also have an on-board DC-DC converter with an integrated LDO. There is a built-in bit synchronizer for clock recovery system, plus automatic channel activity detection (CAD) with ultra-fast automatic frequency control (AFC).

The chip family incorporates a protocol engine that is essentially a dedicated microcontroller. This allows the SPI interface to be used to exchange commands instead of just toggling bits in the modem. This simplified user interface reduces the load on the host processor as well as the developer’s coding chores. Sending and receiving packets can now take as little as 10 lines of C code.

The compact, 4-mm by 4-mm chip supports a frequency coverage of 150 to 960 MHz. It is protocol-compatible with existing deployed LoRaWAN networks.

Chips also support FSK, GFSK, MSK, GMSK, and LoRa modulation. They have programmable bit rates up to 62.5 kbits/s for LoRa and 300 kbits/s for FSK and variants.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: