Speeding the Process of Building IPs, Chiplets, and SoCs

What you’ll learn:

- How IP-XACT enables tool interoperability, multi-level abstraction, and accurate hardware/software interface alignment through structured metadata.

- Why integration automation is critical as complexity increases for SoCs and multi-die systems.

- Why structured IP metadata is essential for integrating IPs, subsystems, and chiplets.

Today’s system-on-chip (SoC) devices are constantly increasing in both size and complexity, often incorporating thousands of intellectual-property (IP) blocks, each containing millions or even billions of transistors. Creating systems of this size and sophistication is mindbogglingly complicated.

To overcome limitations in reticle size and improve yield and scalability, many designs are now disaggregated into multiple dies, or chiplets, that together form a multi-die system within a single package. This rapid growth is driven by the escalating requirements of modern applications. They demand increased processing power and tighter system integration, especially in areas such as artificial intelligence (AI), machine learning (ML), and high-performance computing (HPC).

Another consideration is that SoCs encompass a complex blend of hardware and software components, tightly coupled to deliver high performance, efficiency, and flexibility. The physical manifestation of the hardware-software interface (HSI) is embodied by control and status registers (CSRs) located in the IPs.

The number of CSRs in IPs, SoCs, chiplets, and multi-die systems varies enormously depending on scale and functionality. To provide one point of reference, a high-end SoC can have anywhere from 200K to over 5 million CSRs, each containing multiple fields and bits.

Integration management of all these elements benefits from a coordinated and highly automated design flow. As design complexity increases, so does the need for tools that can accurately align hardware and software, ensure consistency, and reduce the risk of errors throughout the system development process.

The Challenge of Integration Automation

Most of the soft IPs used to create SoCs are typically sourced from trusted third-party IP providers. Similarly, the hard IPs, or chiplets, employed to build multi-die systems are supplied by specialized vendors. The design team will usually develop one or more custom IPs. These internally designed components help distinguish the SoC or multi-die system from its competitive offerings.

Previously, IP providers and design teams often used their own formats, documentation styles, and interface definitions to represent the port and register data associated with the IPs. This data was stored in human-readable documents and spreadsheets. The result was time-consuming, error-prone, and didn’t lend itself to integration automation.

To address the growing challenge of integrating IPs originating from multiple vendors and internal sources, the SPIRIT Consortium developed IP-XACT in the early 2000s. This consortium consisted of major semiconductor and EDA companies, including Arm, Cadence, Mentor, Synopsys, and others. Their work resulted in an XML-based standard used to describe IP metadata, such as interfaces, memory maps, bus protocols, parameters, and register sets, in a machine-readable, tool-agnostic format.

Today, the standard is widely used to facilitate integration automation. IP-XACT is now maintained by the Accellera Systems Initiative, which has absorbed the SPIRIT Consortium and works closely with the IEEE and EDA vendors to maintain and evolve the standard.

IP-XACT 2009, 2014, and 2022

Like all standards, IP-XACT has evolved, with major releases taking place in 2009, 2014, and 2022. Different IP providers and design teams have adopted and may still use the older versions.

IP-XACT 2022 provides a more straightforward and complete schema to support today’s complex IPs and SoCs than the 2009 and 2014 releases. For reference, a high-level comparison with the 2009 release is provided in Table 1, and the 2014 release in Table 2.

IP-XACT at Different Abstraction Levels

The term “IP” can apply to a soft IP block forming part of a monolithic SoC or a larger subsystem composed of multiple soft IPs. It may also refer to hard IP in the form of a chiplet, or even a complete SoC or multi-die system.

To support this range, IP-XACT can be used to create models of individual IPs, multi-IP subsystems, chiplets, and entire SoCs. A high-level view of how this works at different abstraction levels is as follows:

IP Level

- IP-XACT was originally developed to describe individual IP blocks in a standard, tool-interoperable format.

- It defines interfaces, registers, memory maps, ports, and parameters.

Subsystem and Chiplet Level

- IP-XACT can be used to describe subsystems and chiplets made up of multiple interconnected IPs.

- Bus definitions, address maps, interconnects, and component hierarchies can be captured.

SoC and Multi-Die System Level

- An SoC or multi-die system can be described as a top-level component that aggregates lower-level components hierarchically.

- The format supports full interconnect and bus definitions across the system.

- It enables address space definitions across the whole device.

- Register-level descriptions may be included for memory-mapped peripherals.

- Multiple abstraction levels, such as behavioral or RTL views, are supported.

Facilitating Integration Automation

The world is experiencing an insatiable demand for AI and HPC. The electronics industry’s response involves sophisticated SoC and multi-die systems that offer increasing computational capacity and performance. However, these devices are correspondingly more complex.

The creation of IP-XACT models associated with individual IPs and subsystems, which are composed of multiple IPs, facilitates integration automation and speeds up the verification and assembly of higher-level systems.

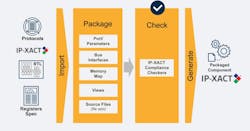

Arteris recently introduced Magillem Packaging, which automates the capture of IP descriptions that meet the latest IP-XACT 2022 standard. As shown in the figure, the tool imports HDL files and ensures a correct-by-construction IP-XACT 2022 autogeneration with the fileSets elaboration. It supports the automatic mapping of the bus protocols and enables comprehensive address map definition.

The tool is of interest to different users, including IP providers and design teams creating IPs, whether in soft IP, such as RTL, or hard IP, like chiplets. It addresses all aspects of connectivity and registers, including views, ports, parameters, bus interfaces, memory maps, address spaces, and register intent.

That’s achieved within a single source of truth environment enabling multi-purpose usage and ensures standard compliance and data consistency through the built-in Magillem checkers suite. In addition, the product can import and export multiple file formats, including IP-XACT 2009, 2014, and 2022. This ability supports users working with both legacy and leading-edge IPs and tools.

About the Author

Insaf Meliane

Product Management and Marketing Director, Arteris

Insaf Meliane is a product management and marketing director at Arteris. Before joining the product team, she was a field application manager, supporting customers with complex SoC design integration. Prior to joining Arteris, she held other design and application engineering roles at leading semiconductor companies.

Insaf earned an engineering degree in microelectronics option system-on-chips from Ecole Nationale Supérieure d’Electronique et de Radioélectricité de Grenoble.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: