Arm Compute Subsystem Aims to Speed Up Automotive AI Chip Design

What you'll learn:

- Differences between domain and zonal architectures.

- Arm’s solution to combat the soaring complexity of automotive SoCs.

- Flexibility: The key to Arm’s foray into automotive-grade AI.

The Zena series of Compute Subsystem (CSS) developed by Arm potentially makes it easier and faster for semiconductor firms, Tier-1 suppliers, and even automakers to create automotive-grade AI silicon.

Software is becoming a bigger battleground in the auto industry, and AI is emerging as a core capability running through every domain of the vehicle. “AI workloads are becoming table stakes,” said Dipti Vachani, senior vice president and general manager of Arm’s automotive unit.

As AI starts to underpin everything from advanced driver-assistance systems (ADAS) to in-vehicle infotainment (IVI), companies are reengineering the car’s internal electrical architecture. They’re all moving more of the computing power out of the electronic control units (ECUs) in every corner of the car and into a smaller set of more “centralized” high-performance modules that resemble something closer to a smartphone or a server.

The chips at the heart of it all are uniquely heterogeneous, packing both high-performance and real-time CPUs, GPUs, DSPs, ISPs, AI accelerators, and high-speed networking onto a single silicon die—often based on advanced nodes such as 3 and 5 nm. But designing these chips is becoming incredibly complex and costly, in large part because the silicon must be automotive-grade. That means it must be rigorously qualified to meet industry standards for safety (ISO 26262) and security (ISO/SAE 21434) in cars.

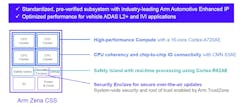

The Zena platform is a pre-integrated and pre-validated set of CPU cores and other building blocks of IP that give its customers a head start on hardware development. This is Arm’s first Compute Subsystem designed for the automotive market. The subsystem consists of a cluster of 16 Cortex-A720AE CPU cores, a real-time Cortex-R82AE CPU core for safety, and a Cortex-M for security—all specifically engineered for the rigors of the road.

To differentiate themselves, customers can attach neural processing units (NPUs), graphics processing units (GPUs), or other custom logic to create a full system-on-chip (SoC) that can run everything from intelligent voice interfaces in the cockpit to advanced safety features.

By dealing with the more undifferentiated facets of the design, Arm said Zena can reduce the silicon development process by up to one year. It is also offering the CSS over the cloud, enabling software development to start before physical silicon is ready.

“This allows customers to focus on the differentiation, whether a silicon provider, Tier-1 supplier, or OEM,” said Vachani.

Differences Between Domain and Zonal Architectures

Arm aims to stay on the front lines of the shift to software-defined vehicles (SDVs) with Zena. It’s all about replacing the fragmented hardware under the hood today with software that can be upgraded over time.

Today, modern vehicles can be burdened with between 100 to 150 electronic control units (ECUs). In general, each one only comes with enough computing power to control the software for a single job, from managing the powertrain to running the dashboard display or driver-assist systems. Developed by a wide range of third-party suppliers, these units typically run proprietary, non-upgradable software, largely inaccessible even to automakers.

But as their numbers rise, integrating them together in the car is becoming increasingly complex. Each ECU requires redundant wiring, contributing to a complex and space-consuming cabling harness system.

The movers and shakers in the auto industry are trying to cut through the complexity by replacing most of the ECUs—and the microcontrollers (MCUs) inside them—with a smaller cluster of high-performance units built on heterogeneous SoCs.

Most traditional automakers such as Toyota and Ford are upgrading to domain architectures, in which every subset of functions—such as the powertrain, chassis, infotainment, and body control—is managed by a dedicated domain controller. Instead of locking every single function to a separate ECU, several functions can run in separate containers or software modules in a single chip. The overhaul opens the door to decoupling hardware from software development, which can reduce the complexity of producing both.

On the other hand, tech giants and startups such as Tesla and Rivian are rewiring everything for the zonal architecture. This approach integrates ECUs based on physical location rather than function.

The zone controllers are placed in different corners or regions of the car and communicate with each other and a central computing unit using fast Ethernet. This more strategic placement reduces the amount of computing hardware in the vehicle and removes more of the heavy and expensive wiring stretching into every corner of the car.

These approaches come with challenges, primarily around software complexity and system integration. But the tradeoff is flexibility. It gives automakers the ability to upgrade or update software-based features via over-the-air (OTA) updates.

Trying to tap into the trend, semiconductor companies such as Intel, NVIDIA, NXP, Qualcomm, and Renesas are racing to roll out high-performance chips that can serve as the brains of future software-defined vehicles.

For instance, NXP’s S32N is the first in a family of what it calls super-integration processors. Based on the 5-nm node more commonly seen in data centers today, it’s designed to act as the “central brain” for real-time vehicle controls, including the powertrain and chassis. It can run a wide range of different functions, even in cases where they belong to different domains, requiring varying degrees of safety and security. Merging these “mixed criticality” systems in a single chip curbs cost and system complexity.

Arm’s Solution to Combat the Soaring Complexity of Automotive SoCs

To stay a step ahead of these technological changes, Arm unveiled its latest line of Automotive Enhanced (AE) CPU cores in 2024, including the Cortex-A720AE, Cortex-R82AE, and many of the other building blocks of IP used in the new Zena subsystem. They’re all based on the same Arm v9 architecture as its CPU blueprints for data centers, while bringing automotive-grade safety and security features into the fold.

Zena mitigates the difficulties of building these CPU cores and other building blocks of IP into automotive-grade chips, which need to fit within tight power and thermal budgets while remaining safe and secure.

The first-generation Zena is based on a high-performance cluster of 16 Arm Cortex-A720AE CPU cores and a safety island featuring a Cortex-R82AE for real-time processing, such as fault management, safety monitoring, system control, and secure boot. Arm said the real-time CPU is specifically designed to run safety-critical operations, enabling up to the ASIL D standard for safety integrity. The platform includes system interconnects like the CME S3AE for CPU coherency and chip-to-chip I/O connectivity.

Zena adds a secure enclave to act as the root of trust (RoT) and secure everything at the chip level.

By pre-integrating all of these hardware building blocks, Arm said Zena helps reduce the engineering burden on chip designers. The company further stated it can reduce the number of engineers needed per project by 20%.

One of the other pros of the new CSS is that it gives automakers and chip firms the ability to reuse more of the hardware and the software that runs on top of it between vehicles. “This is critical because developing custom hardware and software stacks for every vehicle model and application is costly, time-consuming, and burdensome to validate and certify,” said Vachani. He added that the CSS allows partners “to innovate and differentiate on top of a standard platform in areas that add distinct value to their product lines.”

Reducing development cost and complexity is a big deal because Arm underpins the automotive chips used by virtually every top car manufacturer today, including the likes of Honda, Mercedes, Rivian, and Tesla.

Flexibility: The Key to Arm’s Foray into Automotive-Grade AI

By pre-validating the CPU and other fundamental building blocks of the SoC, Vachani said Arm is giving its customers a lot more flexibility to focus on AI and other areas where they can differentiate themselves.

According to Arm, companies can easily integrate partner-specific logic into Zena, including NPUs or other on-die accelerators to handle the rising computational demands of AI. It can also integrate its automotive-grade ISPs to enable more advanced computer vision, including 360-degree surround-view vision for ADAS, and Mali GPUs to run reconfigurable instrument clusters, dashboard displays, and other parts of the digital cockpit.

Furthermore, Zena supports die-to-die communications based on the Universal Chiplet Interconnect Express (UCIe) standard for customers that want to integrate off-die accelerators or other custom-made logic as chiplets.

For instance, Arm said you could use Zena as the core building block in a high-performance chip for Level 2+ ADAS. It merges the CPU with several smaller ISPs to run the cameras and other sensors embedded in the vehicle to sense its surroundings and a relatively large NPU to run the AI at the heart of safety features. Alternatively, you could use the same building block in a domain controller for the digital cockpit, adding a larger GPU to power dashboard displays and a smaller NPU to incorporate AI-based voice and touch interfaces.

Vachani said Arm is focused on giving companies “maximum flexibility” when designing around it. Several Zena units can be integrated within the same monolithic chip or a multi-chiplet package to run a fully autonomous-driving system or other features requiring higher AI performance. “So, across the vehicle, you can leverage the exact same Zena block, giving you scalability in silicon and scalability in software,” added Vachani.

While it’s not part of the first-generation Zena, Arm previously announced the ultra-high-performance Neoverse V3AE CPU, which is already used by NVIDIA in its Thor SoC for automated and assisted driving.

The CSS gives companies a head start not only in hardware development, but also in software integration. Arm said it’s giving engineers the ability to start developing and testing software on top of virtual prototypes of the subsystem in the cloud even before the physical silicon is out, shortening time-to-market by up to two years. The company collaborated with Cadence, Siemens, and Synopsys on the tools for virtual prototyping.

According to Vachani, one of the other advantages of the CSS is that automotive companies can develop and test software on the same Arm v9 architecture in the cloud that will be deployed in the vehicle.

Vachani said that leading automakers—including top EV manufacturers—and semiconductor firms are already working with Zena, and it will be more widely released later in 2025.

About the Author

James Morra

Senior Editor

James Morra is the senior editor for Electronic Design, covering the semiconductor industry and new technology trends, with a focus on power electronics and power management. He also reports on the business behind electrical engineering, including the electronics supply chain. He joined Electronic Design in 2015 and is based in Chicago, Illinois.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: