UCIe 3.0: Scaling Multi-Die Designs to the Next Level

What you'll learn:

- What has changed between UCIe 2.0 and UCIe 3.0?

- Why UCIe matters for enabling next-generation chiplet architectures.

- Where the semiconductor industry goes next in its chiplet ambitions.

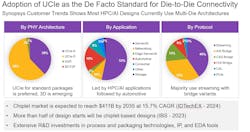

The shift from monolithic system-on-chips (SoCs) toward multi-die designs is rapidly becoming the default way to design a modern chip. As process nodes grow more complex and costly, breaking a large chip into special-purpose, sometimes-smaller dies — commonly known as chiplets — offers advantages in yield, scalability, power efficiency, and time-to-market. However, it also introduces challenges relating to high-speed and reliable die-to-die communication.

The Universal Chiplet Interconnect Express (UCIe) standard addresses this by defining a common interface that allows chiplets from multiple vendors and process technologies to work together seamlessly.

The Rising Complexity of Die-to-Die Communication Underpins UCIe

Prior to UCIe 3.0’s release in mid-2025, UCIe 2.0 laid the foundation for complex chiplet communication, introducing new key features such as:

- Management Transport Protocol (MTP): Enables communication between management entities within a system-in-package (SiP).

- UCIe Debug and Test Architecture (UDA): Architected for chiplet- and package-level testing and debugging.

- UCIe-S Sideband only (SO) port: Permitted for test/manageability purposes in a standard package as an option for a low-speed test port that one can use at the TestChip level.

- x8 (degraded x4) pin module capability for standard packages: Upgraded from version 1.1, which only supports x16 and x64 physical layer interfaces.

- UCIe 3D packaging: Allows for vertical stacking of chiplets and enhances both performance and power efficiency.

However, as multi-die design became the new industry standard, new challenges surfaced. Modern systems now integrate more chiplets per package to meet the needs of applications such as AI and high-performance computing (HPC). This creates more demanding workloads, with each chiplet pushing the limits of bandwidth, latency, and power efficiency. These applications require inter-chiplet links that can move enormous volumes of data with minimal delay and reliable performance.

UCIe 3.0 helps to close that gap by enabling higher speeds, enhanced link reliability, and smarter system coordination for the needs of increasingly complex chiplet packaging.

How UCIe 3.0 is Poised to Power Next-Generation Chiplet Architectures

Doubling the Data Rate

The most notable improvement in UCIe 3.0 is the jump in speed. Doubling the data rate compared to its predecessor from 32 GT/s to 64 GT/s allows for far more bandwidth between chiplets. This higher rate is crucial to implement into production for artificial intelligence, high-performance computing, and multicore processor fabrics, where large amounts of data must move seamlessly across multiple dies. In addition, the speed increase provides a performance boost without a full redesign, making an upgrade easier for existing adopters.

Runtime Recalibration for Link Flexibility

With faster data rates, maintaining signal integrity is increasingly challenging. To address this issue, UCIe 3.0 includes runtime recalibration, a mechanism that allows links to automatically adjust to environmental changes while the system is operating. This feature minimizes the need for guardbands and ensures reliable communication at peak performance levels, making it possible for engineers to maintain signal integrity at double the speed without widening design margins.

Extended Sideband Reach

To support more complex and flexible packaging configurations, UCIe 3.0 extends sideband signaling reach up to 100 mm. This enhancement lets designers connect chiplets that are physically far apart within a package. The result is greater flexibility to optimize die placement and support advanced packaging techniques in complex multi-die layouts.

Early Firmware Download and Deterministic Messaging

Additional new features introduced in UCIe 3.0 include early firmware download and deterministic sideband messaging. Early firmware download was implemented to shorten the booting process by starting firmware transfers earlier in the process. Deterministic sideband messaging sends data signals or carries control to ensure reliable and timely communication, improving responsiveness. Both functions work to improve efficiency and reaction time.

Implementing UCIe 3.0 and What’s Next for Inter-Chiplet Communication

To adopt UCIe 3.0, it’s necessary to integrate the cohesive stack of IP, verification, and design tools to ensure full functionality of the specification. In turn, systems will be able to connect seamlessly across silicon and system boundaries. With the support of a flexible controller IP that enables multiple upper-layer protocols such as PCIe, CXL, and custom streaming interfaces, design teams can tailor their interconnect strategy to match the needs of their workloads and systems.

Verification IP (VIP) solutions model all of UCIe 3.0’s new behaviors from early firmware loading to sideband prioritization, helping engineers with system-level interactions before silicon. When combined with 3DIC design tools, users can create more streamlined and efficient configurations and pathways to manage complex productions.

As chiplets continue to advance to support emerging innovations, UCIe will inevitably evolve in tandem. This will lead to a more efficient and scalable system to power the next wave of semiconductor advances.

>>See our coverage of the 2026 Chiplet Summit, and check out the TechXchange for similarly themed articles and videos

About the Author

Manuel Mota

Senior Manager, Product Management, Die-to-Die IP, Synopsys

Manuel Mota is currently Senior Manager of Product Management for Die-to-Die IP at Synopsys. He holds a Ph.D in electronic engineering from Lisbon Technical University and has held research and technical positions at The European Organization for Nuclear Research (CERN) in Geneva, Chipidea, and MIPS.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: